# Automated Software Synthesis for Streaming Applications on Embedded Manycore Processors

By

### MATIN HASHEMI

B.S. (Sharif University of Technology) 2005M.S. (University of California, Davis) 2008

### DISSERTATION

Submitted in partial satisfaction of the requirements for the degree of

### DOCTOR OF PHILOSOPHY

in

### ELECTRICAL AND COMPUTER ENGINEERING

in the

OFFICE OF GRADUATE STUDIES

of the

UNIVERSITY OF CALIFORNIA

**DAVIS**

Approved:

Soheil Ghiasi, Chair

Venkatesh Akella

Bevan Baas

Committee in Charge

2011

### Abstract

Stream applications are characterized by the requirement to process a virtually infinite sequence of data items. They appear in many areas including communication, networking, multimedia and cryptography. Embedded manycore systems, currently in the range of hundreds of cores, have shown a tremendous potential in achieving high throughput and low power consumption for such applications.

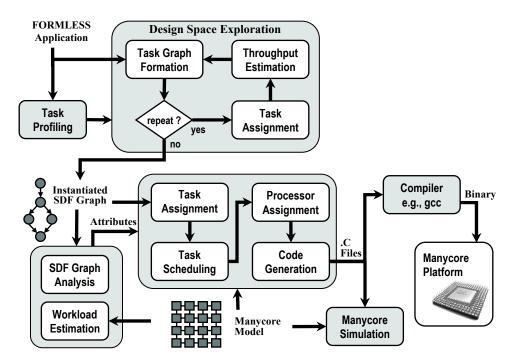

The focus of this dissertation is on automated synthesis of parallel software for stream applications on embedded manycore systems. Automated software synthesis significantly reduces the development and debug time. The vision is to enable seamless and efficient transformation from a higher-order specification of the stream application (e.g., dataflow graph) to parallel software code (e.g., multiple .C files) for a given target manycore system. This automated process involves many steps that are being actively researched, including workload estimation of tasks (actors) in the dataflow graph, allocation of tasks to processors, scheduling of tasks for execution on the processors, binding of processors to physical cores on the chip, binding of communications to physical channels on the chip, generation of the parallel software code, backend code optimization and estimation of throughput.

This dissertation improves on the state-of-the-art by making the following contributions. First, a versatile task allocation algorithm for pipelined execution is proposed that is provably-efficient and can be configured to target platforms with different underlying architectures. Second, a throughput estimation method is introduced that has acceptable accuracy, high scalability with respect to the number of cores, and a high degree of freedom in targeting platforms with different underlying onchip networks. Third, a task scheduling algorithm is proposed, based on iteration overlapping techniques, which explores the trade-off between throughput and memory requirements for manycore platforms with and without FIFO-based onchip communication channels. Finally, to increase the scalability of application throughput with respect to the number of cores, a malleable dataflow specification model is proposed.

### Acknowledgments

I would like to express deep appreciation for my current and previous teachers, mentors and advisers whom I learned a lot form. In specific, I would like to wholeheartedly thank Professor Soheil Ghiasi, my PhD adviser, for his help, support and guidance during the period of my graduate studies at UC Davis. Many thanks to UC Davis faculty for teaching informative courses, and specially Professor Venkatesh Akella and Professor Bevan Baas who also improved this work with their thoughtful comments. I would like to thank the ECE department staff specially Renee Kuehnau and Lance Halsted for their passionate work and supporting of students. The credit for this work partially goes to Po-Kuan Huang, Adam Harbour, Mohammad Hossein Foroozannejad, Lin Chen, Christoph Etzel, Houshmand Shiranimehr, Bin Liu, Mehrdad Afshari and Volodymyr Khibin.

## Contents

| Abstract                                                                        | i     |

|---------------------------------------------------------------------------------|-------|

| Acknowledgments                                                                 | iii   |

| Chapter 1. Introduction                                                         | 1     |

| Chapter 2. Background                                                           | 4     |

| 2.1. Manycore Systems                                                           | 4     |

| 2.2. Dataflow Model                                                             | 5     |

| 2.3. Software Synthesis                                                         | 7     |

| Chapter 3. Task Assignment Techniques for Pipelined Execution of Stream Program | ns 16 |

| 3.1. Terms and Definitions                                                      | 17    |

| 3.2. Attribute Properties and Transformations                                   | 20    |

| 3.3. Versatile Task Assignment via Graph Partitioning                           | 23    |

| 3.4. Approximation Method                                                       | 31    |

| 3.5. Practical Extensions                                                       | 35    |

| 3.6. Empirical Evaluation                                                       | 40    |

| 3.7. Related Work and Chapter Summary                                           | 50    |

| Chapter 4. Scalable Estimation of Application Throughput on Manycore Platforms  | 52    |

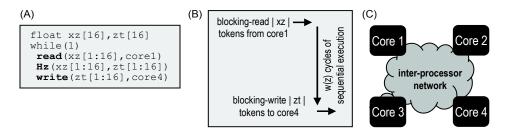

| 4.1. SEAM: Sequential Execution Abstraction Model                               | 53    |

| 4.2. Empirical Evaluation                                                       | 55    |

| 4.3. Related Work and Chapter Summary                                           | 58    |

| Chapter 5. Throughput-Memory Tradeoff via Overlapping Application Iterations    | 60    |

| 5.1. Preliminaries and Definitions                                              | 61    |

| 5.2. Iteration Overlapping                                                      | 66    |

| 5.3. Throughput-Memory Tradeoff                                                 | 75    |

| 5.4.    | Empirical Evaluation                                | 81  |

|---------|-----------------------------------------------------|-----|

| 5.5.    | Related Work and Chapter Summary                    | 82  |

| Chapte  | r 6. Throughput Scaling via Malleable Specification | 85  |

| 6.1.    | Motivating Example                                  | 86  |

| 6.2.    | FORMLESS: A Malleable Dataflow Model                | 88  |

| 6.3.    | Exploration of Forming Parameter Space              | 91  |

| 6.4.    | Empirical Evaluation                                | 95  |

| 6.5.    | Related Work and Chapter Summary                    | 109 |

| Chapte  | r 7. Conclusion and Future Work                     | 110 |

| Bibliog | raphy                                               | 114 |

| Append  | dix A. Benchmark Applications                       | 123 |

### CHAPTER 1

### Introduction

Streaming applications are characterized by the requirement to process a virtually infinite sequence of data items [LP95]. The main quality metric in the streaming domain is throughput, the rate at which data items are processed [GGS+06]. Such applications are becoming increasingly important and widespread. They appear in many areas ranging from communications in embedded sensor nodes, to multimedia and networking in desktops computers, to high-end server applications such as cryptography, hyperspectral imaging and cellular base stations [dK02, MKWS07, TA10]. Because of abundant parallelism and predictable data accesses, they are capable of being efficiently executed on manycore systems [GTA06, AED07].

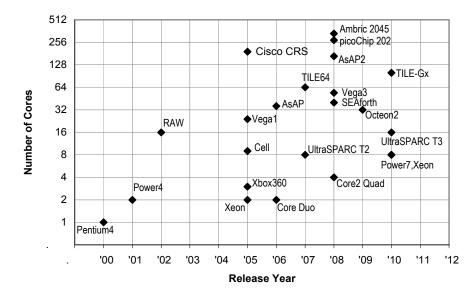

Manycore systems consist of a large number of processor cores interconnected together and behaving as a massively parallel computer system [ABC<sup>+</sup>06, Bor07]. Performance is envisioned to scale mainly through systemwide coarse-grain parallelism. Complicated control and data dependency resolving hardware are likely to be removed in order to open more room for larger number of cores [BHH<sup>+</sup>07, AL07]. While mainstream general purpose processors such as Intel Xeon [SDS<sup>+</sup>11] are currently in the range of ten cores, embedded manycore systems such as Cisco CRS [Eat05], PicoArray [PTD<sup>+</sup>06], TILE64 [BEA<sup>+</sup>08] and AsAP [TCM<sup>+</sup>09] are already in the range of hundreds of cores (Figure 1.1).

Manycore systems have shown a tremendous potential in achieving high throughput and low power consumption for embedded streaming applications [XB08, Pul08, TB10]. Despite this potential, however, the process of stream application development, and embedded application development in general, is largely ad-hoc today [SGM+05, Lee06, HS06]. Presently, the practitioners have to settle for slow and costly development procedures, which are error-prone and yield unportable software [Lee05]. Many researchers are working to develop a formal science to pave the way to systematic and high-confidence development of

FIGURE 1.1. Current trend in the microprocessor design is to increase the number of cores.

embedded applications [SGM<sup>+</sup>05, Mee06]. As a step towards productive stream application development, we focus on automated software synthesis from high-level specifications. Automated software synthesis significantly reduces the development and debug time. The vision is to enable seamless and efficient transformation from a higher-order specification of the stream application to parallel software code (e.g., multiple .C files) for a given target manycore system.

Thread-based specifications often lead to unreliable software [SL05, Lee06], mainly because concurrency constructs in Von Neumann languages introduce nondeterminism into programs [Wen75]. Resolving issues, such as deadlocks, in a flawed multi-threaded program is time-consuming and often requires runtime monitoring [JPSN09, BYLN09]. Dataflow-based high-level specifications, however, address the scalability and productivity issues of parallel threads [TKA02, Lee06]. In this model, the streaming application is described as a set of explicitly-parallel communicating tasks (actors). The rate of communications among the tasks are often known or predictable in the streaming domain [LM87a, TKA02, TKS+05]. Hence, dataflow specifications provide a solid ground for reliable and productive application development through compile-time analysis and optimization algorithms.

In recent years, a number of research groups have worked on automated stream software synthesis from dataflow models to parallel platforms [GTA06, SGB08, HCK<sup>+</sup>09]. Languages such as StreamIt [TKA02] have been developed specifically for this purpose.

In order to automatically realize an application software, a sequence of refinement stages have to be carried out to bridge the gap between high-level dataflow specifications and application implementation. Examples include allocation and scheduling of the tasks on the processors. Chapter 2 presents an overview of different steps normally involved in stream software synthesis from dataflow models to manycore platforms.

The major contribution of this dissertation is presented in Chapters 3 to 6. Chapter 3 presents a versatile dual-processor task assignment algorithm that is provably-efficient and can be easily configured to target platforms with different underlying architectures, and also, a heuristic task assignment method for pipelined architectures. Chapter 4 presents a manycore performance estimation method with acceptable accuracy, high scalability with respect to the number of processors, and high degree of freedom in targeting platforms with different underlying onchip network architectures. Chapter 5 presents iteration overlapping which is a technique in adjusting the execution order of tasks, and is closely related to software pipelining. It greatly improves the scalability of throughput with respect to the number of processors by providing an adjustable knob in trading memory for more throughput. Chapter 6 presents a new dataflow model for specifying stream applications. Gaining insight from our previous works, we concluded that in addition to efficient optimization algorithms, malleable high-level specification models are required in order to achieve high scalability and portability with respect to the number of processors across a wide range of platforms. And finally Chapter 7 concludes this dissertation by presenting an overall summary of the lessons learned and possible directions for future work.

### CHAPTER 2

### Background

Right abstractions are the key in quality software synthesis in the embedded domain [PBSV<sup>+</sup>06]. Sections 2.1 and 2.2 present an overview of the abstract models that we used for the manycore platform and the streaming application specification. Note that in our empirical evaluations, the automatically synthesized codes are compiled and executed on the actual target hardware platform. Section 2.3 presents the optimization steps involved in automated software synthesis from dataflow models to manycore platforms.

### 2.1. Manycore Systems

A traditional parallel processing platform is composed of memory units, processor chips and their interconnection network. A manycore system, however, is fabricated entirely in one chip with the exception of memory which may or may not be integrated on the chip. Similar to the traditional platforms, manycore systems can be classified as shared-memory or distributed-memory. All processor cores have access to the same memory in a shared-memory manycore system, while in a distributed-memory system, the cores can only access their own memory.

The processor cores may cooperate in processing the same data, in which case, locks or similar mechanisms are required for synchronization. This approach is common in thread-based programming (see Section 2.2). Alternatively, the cores may communicate by sending and receiving messages, which is known as the message passing approach.

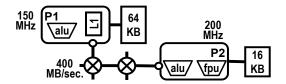

We target execution platforms whose abstract model exposed to the software synthesis process can be viewed as a distributed-memory manycore system in which the processor cores communicate by sending and receiving messages through point-to-point unidirectional FIFO channels. Figure 2.2.A on page 8 illustrates an example system with 4 processor cores in which neighbor cores are connected through FIFO channels. Many existing manycores such as AsAP [TCM<sup>+</sup>08] and Tilera [BEA<sup>+</sup>08] conform to this abstraction. FPGA-based systems can also implement the above model through soft processor cores such as Microblaze

[Mic] or Nios [Nio]. The model is reasonably accurate at high-level for other platforms that implement the abstract view using different underlying architectures.

Systems with shared memory, such as multicore Intel Xeon [RTM<sup>+</sup>09], can be programmed to implement the virtual directed links, for example, with a virtual FIFO as an array in the shared memory space. Systems with on-chip networks, such as IBM Cell [KDH<sup>+</sup>05], can implement the virtual directed links with assistance of system software for buffering and reordering of packets at processors. Note that the implemented communication mechanism has to deliver messages in the order they are sent. Message delivery in deterministic order, e.g. in-order delivery, is required for correct realization of statically scheduled applications.

Our model is a multiple-instruction multiple-data (MIMD) architecture which is conceptually different from a single-instruction multiple-data (SIMD) architecture. Normally, GPU systems are viewed as SIMD machines to parallelize execution of thousands of threads which work on different sections of the data [GLGN<sup>+</sup>08]. However, today's GPU systems are not entirely SIMD. For example, Nvidia Fermi architecture [WKP11] offers up to 512 cores, organized in 16 stream multiprocessor (SM) blocks each with 32 SIMD cores. Inside a block all cores must run the same code, but different blocks may run different codes. Cores located in different blocks may only communicate through the main memory. Therefore, one may view each SM block as one core capable of executing multiple threads of the same task but on different data [HCW<sup>+</sup>10].

Throughout this manuscript, P denotes the total number of processor cores,  $p_k$  denotes the k'th processor  $(1 \le k \le P)$ , and f(k, k') denotes the FIFO channel from  $p_k$  to  $p_{k'}$ .

### 2.2. Dataflow Model

Let us briefly discuss the problems associated with thread-based models before explaining the dataflow model. When two threads try to access and modify a shared object, e.g., memory, the possible data race may result in corrupted values. Unfortunately, current synchronization solutions, e.g., locks, have a fundamental problem. They are not composable, meaning that combination of two correct lock-based codes does not necessarily result in a race-free code. In addition, locks may result in deadlock [SL05]. Multi-threading has been originally designed for server applications which naturally show process-level parallelism,

while some desktop and embedded applications have fine-grained parallelism, complicated interactions, and pointer-based data structures which make them hard to parallelize with threads [SL05]. A number of leading experts believe that thread-based application development in general, is not a productive and reliable method of developing concurrent software [Lee06]. One reason is that concurrency constructs in Von Neumann languages introduce nondeterminism into programs [Wen75].

Dataflow models address the scalability and productivity issues of parallel threads [Lee06]. Here, the streaming application is described as a set of explicitly-parallel communicating tasks (actors). Tasks are atomic, i.e., their corresponding computation is specified in sequential semantics, and hence, intra-task parallelism is not exploited.

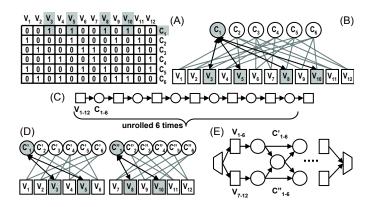

Synchronous dataflow (SDF) is a special type of dataflow in which tasks' data rates are specified statically [LM87a]. SDF-compliant kernels are at the heart of many streaming applications [LM87a, TKA02, GB04] and form the focus of our work. In the SDF model, a task is a tuple

$$(2.1) (In, Out, H)$$

where  $In \subseteq InputPorts$  is the set of input ports,  $Out \subseteq Outputports$  is the set of output ports, and H denotes the transformation function of the task.  $Ports = InputPorts \cup Outputports$ , and  $InputPorts \cap Outputports = \emptyset$ . Each port has a statically-defined data rate, which is the mapping

$$(2.2) rate: Ports \to \mathbb{N}$$

The application is modeled as a directed graph G(V, E), known as task graph, where vertices  $v \in V$  represent tasks, and directed edges  $e \in E \subset Ports^2$  represent data communication channels. Each port is connected to exactly one channel, and each channel connects an output port of some task to an input port of another task.

A task can be executed (fired) upon availability of sufficient data on all its input ports. Firing of a task consumes data from its input ports, and produces data on its output ports. In streaming applications, the execution is meant to continue for infinite number of rounds.

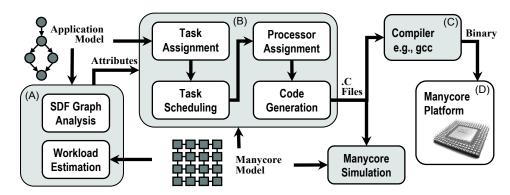

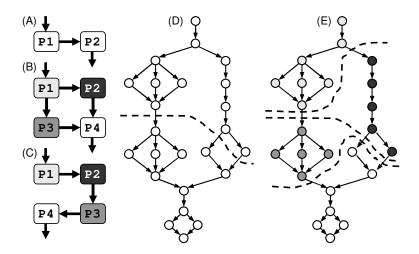

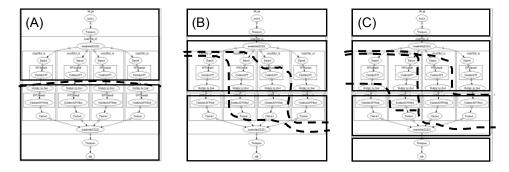

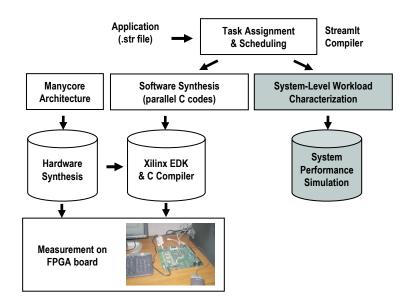

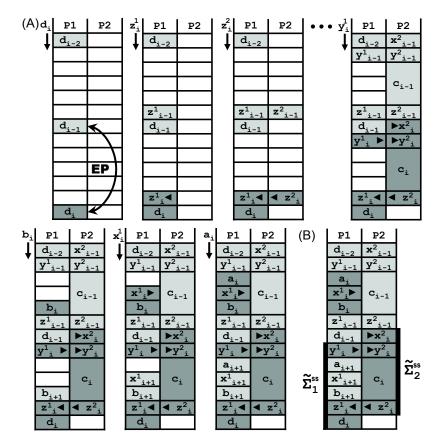

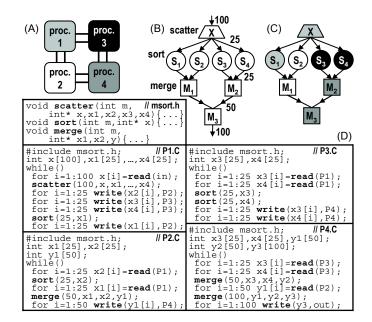

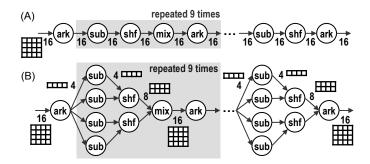

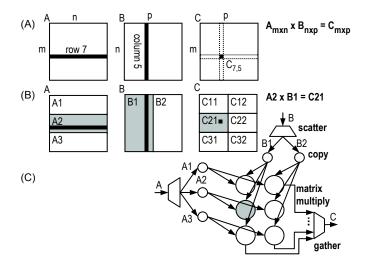

FIGURE 2.1. The big picture of software synthesis based on given application and target manycore models. A) SDF graph analysis and workload estimation steps provide the required information for B) automated synthesize of parallel software modules, which can be subsequently C) compiled, and then D) executed on the target manycore platform.

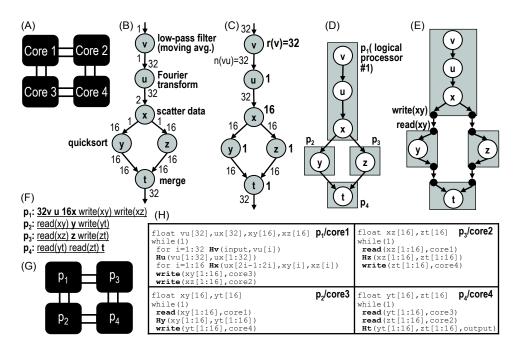

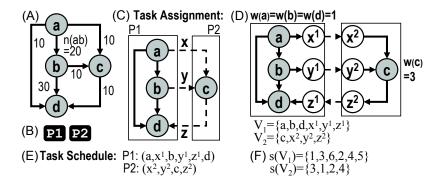

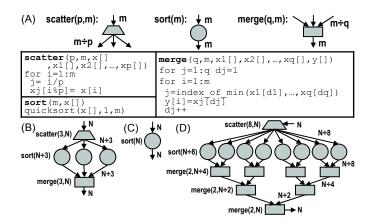

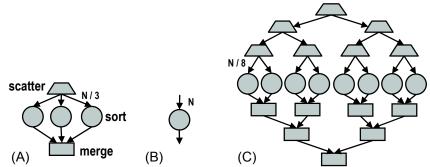

Figure 2.2.B on page 8 illustrates an example SDF model for a toy streaming application that calculates the Fourier transform of a filtered data and subsequently sort the result. The sort is performed by splitting the data in half, sorting each piece with quicksort algorithm and finally merging the two sorted pieces into the final sorted array using the well-known mergesort algorithm [CLRS01b].

### 2.3. Software Synthesis

Given the abstract model of a target manycore architecture and the SDF graph model of an streaming application, parallel software modules are automatically synthesized. As an intentional result of the architecture and application models, synthesized software modules need to directly send and receive messages to synchronize.

The main objective of software synthesis is to maximize throughput which is an important quality metric in the streaming application domain. Other optimization objectives and/or constraints include, but not limited to, judicious use of memory and communication resources on chip.

As shown in Figure 2.1.B, the software synthesis procedure involves several key steps including task assignment, task scheduling, processor assignment and code generation. In order to produce high quality code, such steps require a number of *attributes* for vertices (tasks) and edges (channels) of the SDF graph. As shown in Figure 2.1.A, SDF graph analysis and workload estimation steps provide this information. Once the parallel software

FIGURE 2.2. Example: A) Sample system with 4 processor cores. B) Sample SDF graph for a toy streaming application. C) SDF graph analysis. D) Task assignment. E) Inserting write and read tasks. F) Task scheduling. G) Processor assignment. H) Code generation.

modules are synthesized they can be executed on the target manycore platform (Figure 2.1.D), or alternatively simulated with a manycore simulator. To execute the application, each software module, e.g., C code, should be compiled to a binary code using the target native compiler, e.g., gcc (Figure 2.1.C).

The software synthesis steps in Figure 2.1 are briefly introduced here using a simple example. Figure 2.2.A illustrates an example target platform with 4 processor cores. Figure 2.2.B illustrates a toy streaming application that calculates the Fourier transform of a filtered data and subsequently sort the result. The sort is performed by splitting the data in half, sorting each piece with quicksort algorithm and finally merging the two sorted pieces into the final sorted array using the well-known mergesort algorithm as described in [CLRS01b]. The parallel software modules shown in Figure 2.2.H are produced by performing the following steps.

2.3.1. SDF Graph Analysis. As mentioned above, SDF graph analysis and workload estimation steps provide the graph attributes (Figure 2.1.A). Reader may skip the discussion on the SDF graph attributes and go directly to section 2.3.3 on page 11. The first attribute

is firing repetition of tasks. It is defined as the number of times that a task  $v \in V$  is fired in every round of the periodic application execution, and is denoted with r(v). Formally

$$(2.3) r: V \to \mathbb{N}$$

Channels can have different production and consumption rates. For example in Figure 2.2.B, channel vu has a production rate of 1 but a consumption rate of 32. As a result, the firing repetition r(v) should be different for different tasks. In an SDF graph, r(v) can be calculated solely based on the production and consumption rates as described in [LM87b] in order to satisfy the following condition

$$(2.4) \forall e(v, u) \in E : r(v) \times rate(v.port) = r(u) \times rate(u.port)$$

where v.port and u.port denote the two ports that are connected via channel e. For example as shown in Figure 2.2.C, the rates are assigned such that  $r(v) \times 1 = r(u) \times 32$ . In this example, task v is fired 32 times, task x, 16 times, and all other tasks only once in each round of the periodic execution.

The second attribute is communication volume of channels  $e(v, u) \in E$ . It is defined as the total number of tokens transfered from the producer task v to the consumer task u in every round of the periodic application execution. The communication volume of channel e is denoted with n(e) and can be determined based on the task firing repetitions as the following

(2.5)

$$n: E \to \mathbb{N}$$

$$\forall e(v, u) \in E: n(e) = r(v) \times rate(v.port)$$

For example as shown in Figure 2.2.C, the communication volume of channel vu is equal to n(vu) = 32.

**2.3.2.** Workload Estimation. Another attribute is the workload of a task  $v \in V$  on processor  $p_k$ , which is denoted by  $w_k(v)$ . Formally,

(2.6)

$$w_k : V \to \mathbb{N} \ (k \in [1, P])$$

$$w_k(v) = r(v) \times latency$$

where the latency denotes the execution latency of one firing of task v on processor  $p_k$ . The workload is inherently input-dependent, due to the strong dependency of the tasks' control flow (the transfer function H) with their input data. For example, the execution latency of the quicksort algorithm on a list would partially depend on the ordering of the numbers in the list. Other factors affecting the workload include the optimizations performed during compilation of synthesized software modules, and also, the existence of non-deterministic architecture units such as cache.

The accuracy of task workload estimates is crucial to the quality of software synthesis process specially the task assignment step. Therefore, the estimation method should be carefully designed based on a specific situation. Details of the workload estimation method used in this work are discussed in later chapters. In general, there are two main approaches to workload estimation, namely profiling and code analysis. Profiling-based approached measure the execution latency of tasks at runtime. Therefore, no analysis of the code is required, and also, the effects of compiler optimizations and non-deterministic hardware units such as cache and processor pipeline are better captured. Code analysis, however, can be easily automated to quickly analyze the workload of tasks at compile time without requiring to execute the tasks on the target platform [Sar89, WEE+08]. Unpredictable effects of cache is often higher than the effect of processor pipeline or compiler optimizations. Scratchpad memories for embedded systems have been proposed to replace cache in order to improve predictability and energy consumption [UDB06, NDB09].

The last attribute is memory requirement of tasks and channels which is estimated as well.  $m_k(v)$  refers to the amount of memory required by processor  $p_k$  for instructions of a task  $v \in V$ . For example in Figure 2.2,  $m_k(y)$  is the memory footprint of the quicksort algorithm in processor  $p_k$ . Similarly,  $m_k(e)$  refers to the amount of memory required to allocate the array which stores messages of a channel  $e \in E$ . For example as shown in

| Attribute                | Notation         | Possible Unit |

|--------------------------|------------------|---------------|

| firing <u>repetition</u> | r(v)             | -             |

| <u>n</u> umber of tokens | n(e)             | -             |

| computation workload     | $w_k(v)$         | msec.         |

| required <u>m</u> emory  | $m_k(v), m_k(e)$ | KB            |

FIGURE 2.3. The attributes of vertices (tasks) and edges (channels) of an SDF graph G(V, E), which is provided by the steps shown in Figure 2.1.A

Figure 2.2.H,  $m_1(vu)$  is equal to the amount of memory allocated for tokens of channel vu, i.e.,  $m_1(vu) = n(vu) \times \text{sizeof}(float) = 32 \times 4$ . Estimating the memory requirement is often simple, specially for the embedded streaming applications because they normally do not dynamically allocate data structures of unpredictable size. Figure 2.3 summarizes the above attributes for future reference.

**2.3.3.** Task Assignment. Every task should be assigned to a processor for execution. At this point, the physical location of processors on the chip is ignored [SK03]. In other words, tasks are assigned to logical processors in this step, and later in the processor assignment step, logical processors are assigned to the physical processors on the chip. Figure 2.2.D illustrates an example task assignment in which tasks u, v and x are assigned to logical processor  $p_1$ , p to  $p_2$ , p to  $p_3$  and p to  $p_4$ .

When the producer and consumer tasks of a channel are assigned to different processors, the tokens on this channel should be transferred using the platform FIFO channels. This is modeled by adding new write and read tasks to the graph. For example as shown in Figure 2.2.E, for channel xy from  $p_1$  to  $p_2$ , new write and read tasks are added to the graph. Adding the new communication tasks greatly impacts the degree of freedom for task scheduling (more details on this subject in Section 2.3.4 on the next page).

The main objective of task assignment is to judiciously distribute the workload among the processors in order to maximize throughput. This requires the workload attributes  $w_k(v)$ , i.e., the workload of task v if it is allocated on processor  $p_k$ . Task assignment is simpler for manycore systems with identical cores  $[\mathbf{G}^+\mathbf{02}]$ , while in heterogeneous manycore systems the difference among the cores should also be considered for efficient implementation  $[\mathbf{VR99}, \mathbf{SK03}, \mathbf{MK08}]$ . Depending on the target architecture, task assignment may involve additional objectives and/or constraints. For example, minimization of interprocessor communication overhead is often a second optimization objective specially since it normally affects the throughput  $[\mathbf{SBGC07}, \mathbf{HG09}]$ . This requires the use of attributes n(e). Another example is when onchip memory is limited, in which case, the memory requirement of each processor can be added as a constraint. This requires the use of attributes m(v) and m(e). If the required memory exceeds the available local memory the implementation is infeasible, and hence, the estimated performance gain through workload balancing

is irrelevant. However, most task assignment approaches focus mainly on workload in order to increase the throughput and consider the memory limits only as a second constraint if at all. This is because there are often a number of ways to spill data in and out of the limited local memory [UDB06, HCK<sup>+</sup>09], but note that such approaches often work only for the data memory and not the instruction memory.

Task assignment for a manycore target with P processors can be formulated as a graph partitioning problem in which the graph should be partitioned into P subgraphs. An example partitioning objective is to evenly distribute weights of the vertices (task workloads) while minimizing weight of cut edges (communications) [MK08, HG10]. Other approaches include ILP-based task assignment formulations which normally provide higher degree of freedom in defining a heterogeneous architecture but may take longer to execute [HCK<sup>+</sup>09]. Heuristic task assignment methods often sort the tasks first and allocate them on the processors in that order. The criteria for sort is normally either the task workloads alone or a combincation of workloads, communication overheads and memory requirement [G<sup>+</sup>02, SBGC07].

**2.3.4.** Task Scheduling. Assuming each core executes only one thread, which is the case in our hardware model, tasks that are assigned to the same processor should be ordered for sequential execution on that processor. In SDF model, the production and consumption rates are known at compile-time and hence such ordering can be determined statically [LM87b]. Figure 2.2.F shows a valid schedule for each of the logical processors in our example. Note that the execution is periodic, for example the schedule [read(xy), y, write(yt)] for processor  $p_2$  means the following sequence repeats periodically. The data on channel xy is first read from FIFO, task y is executed, and then the data produced on channel yt are written to FIFO.

Communications between tasks that are assigned to different processors cause interprocessor dependencies, and hence, scheduling of the tasks on one processor is not independent from scheduling of the tasks on other processors. Failure to consider this effect may result in a deadlock situation [**ZL06**]. Task scheduling should avoid deadlock by considering the dependency of a task in every processor with the tasks in other processors. This is

closely related to the effect of FIFO channels especially when cycles exist in the dataflow graph [GGB<sup>+</sup>06, SGB08, LGX<sup>+</sup>09, PD10].

Besides deadlock avoidance, the main optimization objective of task scheduling, however, is to maximize throughput by judiciously scheduling the tasks in time. Inter-processor dependencies should be carefully analyzed at compile-time in order to avoid idle periods in the execution. Iteration overlapping, a.k.a. pipeline parallelism [GTA06, KM08], is a technique that alters the task schedule by overlapping the execution of different iterations of the streaming application in order to fill the idle gaps. This is closely related to software pipelining where multiple iterations of a loop are overlapped [Rau94]. Insertion of new write and read communication tasks to the task graph (Section 2.3.3) provides more room for such optimizations because it disentangles the execution of a task from its dependent consumers (or producers) in other processors, and it also disentangles the consumers of the task from one another.

As opposed to task assignment where throughput and memory requirements are often considered as separate factors, in task scheduling the two have a strong relation [BLM96, BML99]. In other words, the schedule of tasks directly impacts both the throughput and the memory requirement at the same time. The reason for the impact on memory is that the local buffering requirement of a channel vary depending on how far its producer or consumer tasks are located in the schedule of that processor, and how many times the task executes on every iteration of the periodic execution [ZTB00, KTA03, KMB07].

Hence, memory requirement may be taken into account as a constraint when onchip memory is limited. Note that when tasks are coarse-grain, e.g., functions, as opposed to fine-grain, e.g., instructions, multiple calls to the function are inserted into the code instead of multiple copies of the same instruction sequence. In other words, the impact of scheduling on instruction memory is limited for coarse-grain task graphs. Data memory requirement, however, has a strong dependency to the schedule as mentioned above. Therefore, when onchip memory is limited, it would be a wise option to consider instruction memory requirements during task assignment, and data memory requirements during task scheduling.

2.3.5. Processor Assignment. In the task assignment step, tasks are assigned to logical processors, and in this step which is also known as layout or processor binding, the logical processors are assigned to physical processors on the chip [G+02, HM05]. This approach simplifies the problem of assigning tasks to the processors by dividing it in two sub-problems. Hence, faster and more efficient optimization methods could be designed for each of the two steps. Processor assignment considers the effect of onchip communications on the throughput and try to assign communicating processors as close to each other as possible to avoid network congestion. The optimizations required in this step highly depends on the underlying architecture of the onchip network. For example, in manycore systems like AsAP [TCM+08] where onchip communication resources are limited sophisticated algorithms are required to achieve a feasible and high throughput implementation.

In certain cases, task assignment may also need to be aware of the limitations in the onchip network. For example in the first version of AsAP [YMA<sup>+</sup>06], each processor could communicate with only its four neighbor processors. Task assignment for such platforms should consider this limitation in grouping the tasks, or otherwise it may not be possible for the processor assignment step to find a feasible solution.

An alternative way, however, would be to combine task assignment and processor assignment in one step. This is more favorable when the target manycore system has a high degree of heterogeneity. Task assignment needs to be aware of the exact processor architecture in order to have a workload estimate of that task or its memory size constraints. If the degree of heterogeneity is low it may still be favorable to have separate task assignment and processor assignment steps.

2.3.6. Code Generation. Task functionalities are provided as sequential computations that are kept intact throughout the synthesis process. The software code for each processor is synthesized by stitching together the set of tasks that are assigned to that processor according to their schedule. For tasks that are assigned to the same processor, inter-task communication is implemented using arrays. That is, the producer task writes its data to an array, which is then read by the consumer task. Inter-processor communication is implemented using the new write and read tasks inserted in the task assignment step. Figure 2.2.H on page 8 illustrates an example.

Decades of effort have been put into design of efficient sequential compilers such as gcc [BGS94]. To harness the power of optimization algorithms in sequential uni-processor compilers, the code generation only produces a source code, e.g., C file, for each processor core. A native compiler of the target platform can later compile this code into binary. During the uni-processor compilation, specific I/O instructions or calls to certain OS services or library functions may need to be inserted into the binary code to implement the interprocessor communications.

Task workloads, task schedules, production and consumption rates and many other attributes of the automatically synthesized software modules are known at this point. This enables efficient deployment of source-level optimizations which otherwise would not be possible or very difficult and inefficient. Buffer merging is a technique which reduces the data memory requirement. Through careful analysis of the time intervals at which buffers are alive, the source code is transformed such that allocated memory of the buffers overlap [MB04, FHHG10, FHHG11]. In order to reduce energy consumption, workload and scheduling information may assist automatic insertion of DVS (dynamic voltage scaling) instructions into the code [LBDM02, IHK04, FRRJ07].

### CHAPTER 3

# Task Assignment Techniques for Pipelined Execution of Stream Programs

The main objective of task assignment is to optimally distribute the workload among the processors in order to maximize the application throughput. Depending on the target architecture, task assignment may involve additional objectives and/or constraints including but not limited to judicious use of limited onchip memory or minimization of inter-processor communication.

In this chapter, we first present a task assignment method for heterogeneous soft dualprocessor systems. The objective is to maximize throughput, under the constraint that

generated code for a processor meets processor's instruction and data memory size constraints, if needed. Given the high-degree of heterogeneity in the system, different architectures are likely to impact application throughput differently. Optimal mapping of

application tasks onto processors depends on the specifics of the architectures. Ideally, one

would want to have a versatile software synthesis solution that can be parameterized to

target different configurations. Specifically, we present a formally-versatile dual-processor

task assignment algorithm whose formal properties hold for, and hence it is applicable to,

a variety of target hardware platforms with different implementation-driven objectives and

constraints. Leveraging the graph theoretical properties of applications task graphs, we

develop a provably-effective task assignment algorithm that both maximizes throughput,

and guarantees meeting instruction and data size constraints according to high-level estimates. Measurement of generated code size and throughput of emulated systems validate

the effectiveness of our approach [HHG07, HG10].

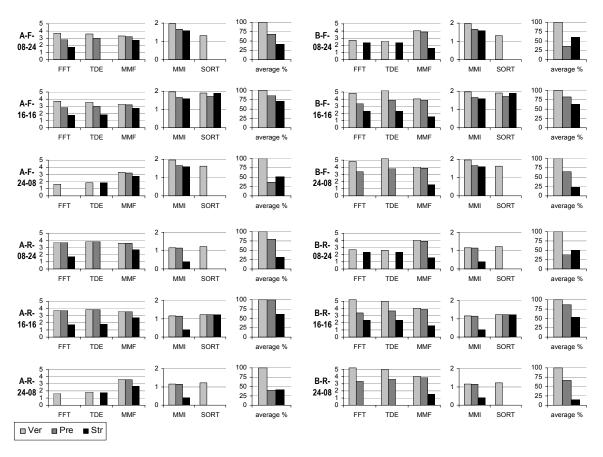

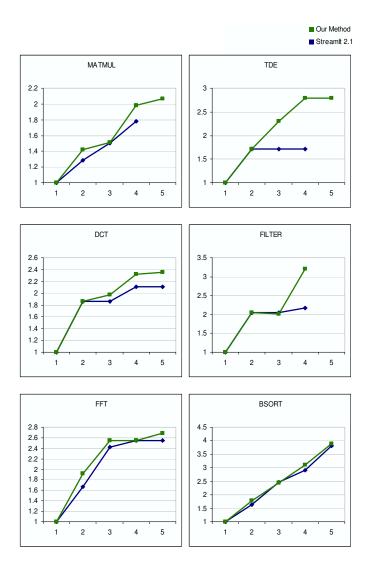

Next, based on the above dual-processor algorithm, we develop a heuristic method for pipelined execution on targets with an arbitrary number of identical processors. In other words, we view the target platform as a chain of processors, and iteratively apply the graph bi-partitioning method (dual-processor task assignment) to partition the task graph among all the processors. Throughput measurement of the generated code on emulated systems validate the effectiveness of our approach [HG08, HG09].

#### 3.1. Terms and Definitions

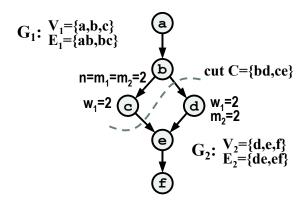

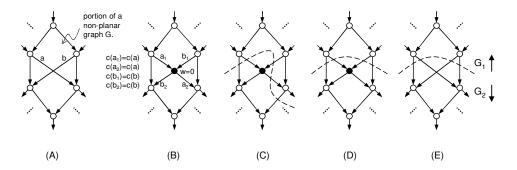

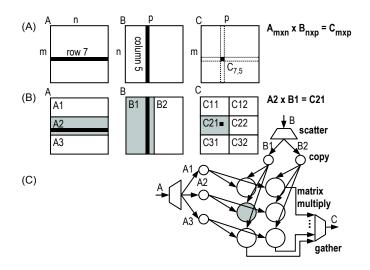

Task assignment for dual-processor platforms can be viewed as bi-partitioning of application task graph, in which tasks in the same partition are assigned to the same processor. A partitioning of graph G(V, E) is constructed by removal (cutting) of a subset of edges (channels) to create two connected subgraphs  $G_1(V_1, E_1)$  and  $G_2(V_2, E_2)$ . We use the term cut C to refer to such cut channels. Formally

$$(3.1) V_1 \cup V_2 = V$$

$$E_1 \cup E_2 \cup C = E$$

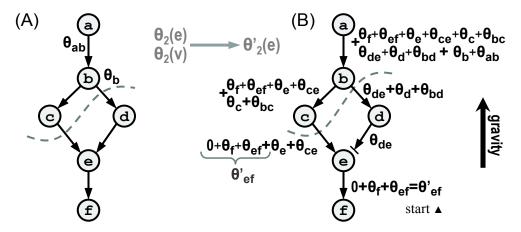

As discussed in the previous chapter (Figure 2.3 on page 10), the task graph is annotated with a number of attributes. Figure 3.1 shows an example task graph in which all the attributes  $w_1$ ,  $w_2$ , n,  $m_1$  and  $m_2$  are equal to 1, except for those shown in the figure. Later in Section 3.5, we discuss extensions to handle other attributes, if necessary. The attributes are naturally extended to partitions in the following manner.

Computation: The total workload of tasks, excluding the extra write and read tasks, assigned to processor  $p_k$ , i.e., in a partition  $G_k$ , is equal to<sup>1</sup>

(3.2)

$$||w_k(V_k)|| = \sum_{v \in V_k} w_k(v)$$

For example in Figure 3.1,  $V_1 = \{a, b, c\}$  and thus  $||w_1(V_1)|| = w_1(a) + w_1(b) + w_1(c) = 1 + 1 + 2 = 4$ .

**Communication:** If a channel e(u, v) is cut, tasks u and v are assigned to different processors, and thus the corresponding communication between u and v has to pass through the on-chip network. The term ||n(C)|| refers to the total number of messages transferred over all the cut channels. In Figure 3.1,  $C = \{bd, ce\}$  and thus ||n(C)|| = n(bd) + n(ce) = 1 + 1 = 2.

<sup>&</sup>lt;sup>1</sup>Throughout this manuscript, for a function  $f: X \to \mathbb{N}_0$ , the term f(X) denotes the set of f(x) values for every x, i.e.,  $f(X) = \{f(x) | x \in X\}$ . For example,  $w(V_k) = \{w(v) | v \in V_k\}$ . The term  $\|f(X)\|$  denotes the  $L_1$  norm of f(X) which is equal to  $\sum_{x \in X} f(x)$ . For example,  $\|w(V_k)\| = \sum_{v \in V_k} w(v)$ . The term |X| denotes the number of elements in a set X.

FIGURE 3.1. An example task graph in which all the attributes  $w_1$ ,  $w_2$ , n,  $m_1$  and  $m_2$  are equal to 1, except for those shown in the figure. Cut  $C = \{bd, ce\}$  divides the graph G in two partitions  $G_1$  and  $G_2$ .

| $  w_k(V_k)   = \sum_{v \in V_k} w_k(v)$                                                                               | computation workload assigned to processor $p_k$                                                                             |

|------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| $  n(C)   = \sum_{e \in C} n(e)$                                                                                       | # of message transferred<br>between processor 1 and 2                                                                        |

| $  m_k(V_k)   = \sum_{v \in V_k} m_k(v)$ $  m_k(E_k)   = \sum_{e \in E_k} m_k(e)$ $  m_k(C)   = \sum_{e \in C} m_k(c)$ | memory required by processor $p_k$ for: - tasks - inter-task intra-processor communications - inter-processor communications |

FIGURE 3.2. Partition attributes are natural extension of vertex and edge attributes.

**Memory:** Cut channels demand allocation of data memory on both processors. The term  $||m_k(C)||$  refers to the amount of data memory allocated for the cut channels on processor  $p_k$ . In Figure 3.1,  $||m_1(C)|| = m_1(bd) + m_1(ce) = n(bd) \times \text{sizeof}(datatype) + n(ce) \times \text{sizeof}(datatype) = 1 + 1 = 2.$

The rest of the channels allocate memory in only one processor. The term  $||m_k(E_k)||$  refers to the total amount of memory required by processor  $p_k$  for implementing intraprocessor communication, in which  $E_k$  represents the subset of channels that are allocated to processor  $p_k$ . In Figure 3.1,  $E_1 = \{ab, bc\}$ , and thus,  $||m_1(E_1)|| = m_1(ab) + m_1(bc) =$ 1+2=3. Similarly, the term  $||m_k(V_k)||$  denotes the amount of instruction memory required by processor  $p_k$  for task set  $V_k$ . The partition attributes are summarized in Figure 3.2 for future reference. 3.1.1. Problem Statement. We target task graphs that contain no cycles. If a given task graph contains a cycle, we collapse the vertices in the cycle into a single task to represent the application as a directed acyclic graph (DAG). Such task graphs form an important subset, because many important streaming kernels can be represented in this fashion. Hence, we aim to assign tasks to processors such that one processor would always send and the other would always receive message. This uni-directional flow of data intuitively suits pipelined throughput-driven execution of streaming applications In the graph domain, this translates to convex cuts, which refer to cuts that connect vertices in  $G_1$  to vertices in  $G_2$  (and not the other way around). Convex cuts, which form the focus of our work in this chapter, characterize a subset of possible task assignments. If all task assignment possibilities were to be considered, task scheduling had to be combined with task assignment to allow evaluation of candidate solutions.

Tasks in the partition  $G_k$  will be assigned to, and executed by processor  $p_k$ , and messages on cut channels  $e \in C$  will be transferred between processors using the onchip network. Hence, task assignment for dual-processors can be formally defined as the following optimization problem:

(3.3) minimize:

$$Q = F(\|w_1(V_1)\|, \|w_2(V_2)\|, \|n(C)\|)$$

$$b) \text{ constraint:}$$

$$\|m_1(V_1)\| + \|m_1(E_1)\| + \|m_1(C)\| \le \text{ memory of processor } 1$$

$$\|m_2(V_2)\| + \|m_2(E_2)\| + \|m_2(C)\| \le \text{ memory of processor } 2$$

That is, the goal is to find the cut C which, (a) maximizes throughput and, (b) meets the processors' memory size constraints. The cost function Q models application execution period, which is the inverse of its throughput. The execution period depends on processor workloads and inter-processor communication. The specific relation, however, depends on the underlying hardware. Our goal is to devise a versatile method to handle a wide variety of cost functions.

For example in a system with negligible interprocessor communications, it may be accurate enough to estimate the execution period as  $Q = F(||w_1(V_1)||, ||w_2(V_2)||) = \max\{||w_1(V_1)||, ||w_2(V_2)||\}$ , because the pipeline throughput would be limited by the slowest of the two

processors. This simplified cost function promotes balancing processors' workload, which has been the focus of most classical task assignment schemes. As another example, assume a sufficiently-buffered FIFO link between the two processors implements the virtual network. A reasonable estimation function would be  $Q = \max\{\|w_1(V_1)\| + \alpha_1\|n(c)\|, \alpha_2\|n(c)\| + \|w_2(V_2)\|\}$ , where  $\alpha_k$  is the extra cycles in workload of processor  $p_k$  to push (pop) one unit of data to (from) the FIFO.

In practice, out of two solutions with identical workload distributions, the one with smaller inter-processor communication is always preferred. Therefore, without loss of generality we assume that the cost function Q is non-descending in ||n(c)||.

### 3.2. Attribute Properties and Transformations

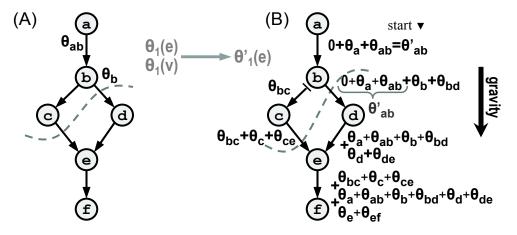

In this section, we exploit structural properties of task graphs to develop a transformation on the attributes, that assists us in quick evaluation of a cut. Let us assume an imaginary attribute  $\theta_1$  is assigned to both tasks (vertices) and channels (edges) in the graph G(V, E). Our objective is to transform  $\theta_1$  to a new set of attributes,  $\theta'_1$ , assigned only to edges of G, such that their summation on any cut would give the summation of the original  $\theta_1$  attributes on vertices and edges in partition 1.

Let  $e_i$  and  $e_o$  denote the set of incoming and outgoing edges of a vertex, respectively. Let  $e_o^*$  be a randomly-selected outgoing edge. The transformed attributes  $\theta_1'$  for outgoing edges of a vertex are recursively defined as follows:

(3.4)

$$\forall v \in V : \theta'_1(e_o) = \begin{cases} \sum_{e_i} \theta'_1(e_i) + \theta_1(v) + \theta_1(e_o) & \text{if } e_o^* \\ \theta_1(e_o) & \text{otherwise} \end{cases}$$

Figure 3.3 shows an example. Intuitively speaking, attribute transformation works similar to gravity. The task graph can be viewed as a physical structure in which every element has a weight, i.e.,  $\theta_1(v)$  and  $\theta_1(e)$  can be viewed as the weight of vertex v and edge e, respectively. Hence, the random selection of one outgoing edge is analogous to disconnecting the corresponding joint in the structure. That is, every vertex stays connected to exactly one of its outgoing edges in the physical domain. The amount of weight held by edge e determines the value of  $\theta'_1(e)$ . In Figure 3.3, edge ab holds  $\theta'_1(ab) = \theta_1(a) + \theta_1(ab)$  of weight. Vertex b in the figure is disconnected from edge bc, and therefore, total weight of vertices a

FIGURE 3.3. A) Sample task graph with attributes  $\theta_1$  for vertices and edges. B) The task graph after transforming  $\theta_1$  to  $\theta'_1$ .

and b and edges ab and bd is held by edge bd. Note that this joint disconnection is only an intuitive analogy, i.e., none of the edges are actually removed or disconnected.

As expected from the gravity analogy, the transformation satisfies our objective property. That is, the sum of  $\theta'_1$  attributes on cut C is equal to the sum of  $\theta_1$  attributes on the edges and vertices of the top partition of graph,  $G_1(V_1, E_1)$ . Intuitively, the cut edges have to hold the entire weight above them. In Figure 3.3,  $\theta'_1(bd) + \theta'_1(ce)$  is equal to  $\{\theta_1(a) + \theta_1(b) + \theta_1(c)\} + \{\theta_1(ab) + \theta_1(bc)\} + \{\theta_1(bd) + \theta_1(ce)\}$ .

Lemma 3.1. The transformation propagates the attribute of an arbitrary vertex (edge) along exactly one directed path, referred to as the propagation path, from the vertex (edge) to the unique sink vertex.

PROOF. Let a be an arbitrary vertex in the directed acyclic graph. The transformation propagates  $\theta_1(a)$  along exactly one of its outgoing edges, which is selected at random. Let b be the destination vertex of the randomly-selected outgoing edge. If b is the sink vertex, then the lemma is proved. Otherwise,  $\theta_1(a)$  is propagated along exactly one of the outgoing edges of b, and the same argument can be made iteratively. Since graph is acyclic, we will never visit a vertex that we have visited before. The graph has finite number of vertices and hence, the iteration will have to end by arriving at the sink vertex. Similar argument can be made for edge attributes.

Theorem 3.2. For a convex cut on a directed acyclic graph

(3.5)

$$\underbrace{\sum_{v \in V_1} \theta_1(v) + \sum_{e \in E_1} \theta_1(e) + \sum_{e \in C} \theta_1(e)}_{weight \ of \ weight \ of \ weight \ of \ total \ weight} = \underbrace{\sum_{e \in C} \theta_1'(e)}_{total \ weight}$$

$$G_1 \ vertices \qquad G_1 \ edges \qquad cut \ edges \qquad held \ by \ cut \ C$$

The theorem should be intuitive from the gravity analogy, in which the weight of every vertex or edge in  $G_1$  is held by one and only one of the cut edges. For example in Figure 3.3, weight of vertex a (i.e.,  $\theta_1(a)$ ) is held by the cut edge bd, and not by ce. Therefore, across all the cut edges, weight of vertices and edges in  $G_1$  are considered exactly once.

PROOF. We argue that C and the propagation path of an arbitrary vertex  $a \in G_1$  intersect at exactly one edge. If C and the propagation path of vertex a do not intersect, then  $a \in G_1$  is connected to the sink vertex via a connected path and hence, C is not a cut. If they intersect in more than one edge, then the propagation path direction goes out of  $G_1$  and then back into  $G_1$ , which means that C is not convex. Therefore, the two edge set intersect at exactly one edge, and hence,  $\theta_1(a)$  is accurately captured in  $\theta'_1$  of the edge. Similar arguments can be made for arbitrary edges in  $G_1$  or C.

We also introduce another transformation similar to above, with the minor difference that the gravity is replaced with a force away from (as opposed to toward) the bottom of the graph. In other words, the graph can be temporarily held upside down. Here, we convert  $\theta_2$  attributes to a new set of  $\theta'_2$  attributes assigned to the edges. Figure 3.4 shows an example.

Theorem 3.3. Similarly we have:

(3.6)

$$\underbrace{\sum_{v \in V_2} \theta_2(v) + \sum_{e \in E_2} \theta_2(e) + \sum_{e \in C} \theta_2(e)}_{\text{weight of}} + \underbrace{\sum_{e \in C} \theta_2(e) + \sum_{e \in C} \theta_2(e)}_{\text{weight of}} + \underbrace{\sum_{e \in C} \theta_2(e) + \sum_{e \in C} \theta_2(e)}_{\text{total weight}}$$

$$G_2 \text{ vertices} \quad G_2 \text{ edges} \quad \text{cut edges} \quad \text{held by cut } C$$

PROOF. Construct a new graph  $G^r$  from G by reversing the direction of all edges, and then, apply Theorem 1 to  $G^r$ .

FIGURE 3.4. A) Sample task graph with attributes  $\theta_2$  for vertices and edges. B) The task graph after transforming  $\theta_2$  to  $\theta_2'$ .

COROLLARY 3.4. By combining Theorems 3.2 and 3.3 we have

(3.7)

$$\sum_{v \in V_k} \theta_k(v) + \sum_{e \in E_k} \theta_k(e) + \sum_{e \in C} \theta_k(e) = \sum_{e \in C} \theta'_k(e)$$

which can be written as

(3.8)

$$\|\theta_k(V_k)\| + \|\theta_k(E_k)\| + \|\theta_k(C)\| = \|\theta_k'(C)\|$$

for  $k \in \{1, 2\}$ .

### 3.3. Versatile Task Assignment via Graph Partitioning

We approach task assignment as a graph partitioning instance, and develop an algorithm that is provably optimal in minimizing cost function Q, or equivalently, maximizing pipeline throughput. The technique is versatile and can optimize a variety of cost functions inspired by different hardware configurations. For clarity, we present our technique using the attributes discussed in Section 3.1. Later in Section 3.5, we will present extensions to our approach.

**3.3.1.** Applying Attribute Transformation. As summarized in Figure 3.2, to obtain the value of partition attributes all vertices or edges in the partition have to be enumerated. For example, one has to enumerate all vertices in  $G_1$  to calculate  $||w_1(V_1)||$ . It would be more efficient to evaluate Equation 3.3 by only processing attributes of the edges in cut C. Here we apply the attribute transformation, and as a result, we will have a new set of

attributes (e.g.,  $w'_1$  instead of  $w_1$ ), which have the desired property. The transformation is applied to the following attributes. Figure 3.5 provides a summary.

**Computation:**  $w_k$  attributes are transformed to a new set of attributes called  $w'_k$ . In this case, " $\theta$ " is mapped to "w", which means,  $\theta_k(v) = w_k(v)$ ,  $\theta_k(e) = 0$  and  $\theta'_k(e) = w'_k(e)$ . Based on Corollary 3.4, we have:

$$||w_k(V_k)|| = ||w'_k(C)||$$

For example in Figure 3.6.A, we need to sum up the workload of vertices a, b and c to calculate  $||w_1(V_1)|| = w_1(a) + w_1(b) + w_1(c)$  from the original graph. After the transformation (Figure 3.6.B), we can obtain  $||w_1(V_1)||$  by enumerating edges bd and ce, i.e.,  $||w'_1(C)|| = w'_1(bd) + w'_1(ce) = \{w_1(a) + w_1(b)\} + \{w_1(c)\}$ . Thus, we use  $||w'_1(C)||$  instead of  $||w_1(V_1)||$ .

**Communication:** Since  $||n(C)|| = \sum_{e \in C} n(e)$ , it is already calculated by looking only at the cut edges, and thus, we do not need to apply the transformation to attributes n.

**Memory:** Attributes  $m_k$  are transformed to a new set of attributes called  $m'_k$ . Here,  $\theta_k(v) = m_k(v)$ ,  $\theta_k(e) = m_k(e)$  and  $\theta'_k(e) = m'_k(e)$ . Based on Corollary 3.4, we have

For example, the memory requirement of processor 2 is originally calculated by visiting vertices f, e and d, and edges ef, de, bd and ce, i.e.,  $||m_2(V_2)|| + ||m_2(E_2)|| + ||m_2(C)|| = \{m_2(f) + m_2(e) + m_2(d)\} + \{m_2(ef) + m_2(de)\} + \{m_2(bd) + m_2(ce)\}$  (Figure 3.6.A). After the transformation, we can derive the same value from  $m'_2(bd) + m'_2(ce)$  (Figure 3.6.B). Thus we use  $||m'_k(C)||$  instead of  $||m_k(V_k)|| + ||m_k(E_k)|| + ||m_k(C)||$ .

Following transforming the attributes, we have a new set of edge attributes, n(e),  $w'_1(e)$ ,  $w'_2(e)$ ,  $m'_1(e)$  and  $m'_2(e)$ , that are summarized in Figure 3.5. They enable evaluation of both the cost function and memory constraint by enumeration of the edges in cut C. Therefore, our target task assignment problem can be cast as finding the cut in the graph, subject to the following objective and constraints:

(3.11) a) minimize:

$$Q(C) = F(\|w_1'(C)\|, \|w_2'(C)\|, \|n(C)\|)$$

b) constraints:  $\|m_1'(C)\| \le \text{memory of processor } 1$

$\|m_2'(C)\| \le \text{memory of processor } 2$

| $	heta_k 	o 	heta_k'$                                                    | Corollary 3.4                                            | Calculation              |

|--------------------------------------------------------------------------|----------------------------------------------------------|--------------------------|

| $\theta_k(v) = w_k(v) \theta'_k(e) = w'_k(e)$                            | $  w_k(V_k)   =   w'_k(C)  $                             | $\sum_{e \in C} w_k'(e)$ |

| transformation not required                                              | n(C)                                                     | $\sum_{e \in C} n(e)$    |

| $\theta_k(v) = m_k(v) \\ \theta_k(e) = m_k(e) \\ \theta_k'(e) = m_k'(e)$ | $  m_k(V_k)   +   m_k(E_k)   +   m_k(C)   =   m'_k(C)  $ | $\sum_{e \in C} m_k'(e)$ |

FIGURE 3.5. Applying attribute transformation to the application task graph.

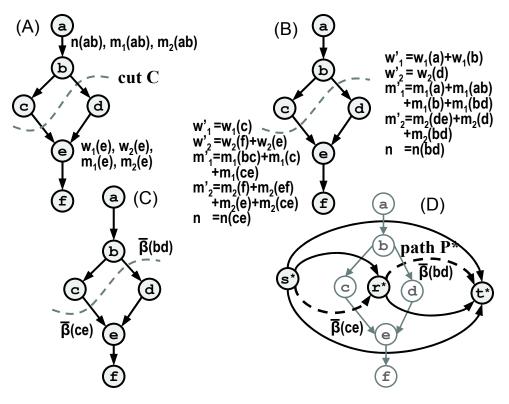

To simplify the notation, we represent the attributes in an attribute vector  $\vec{\beta}(e) = [w_1'(e), w_2'(e), m_1'(e), m_2'(e), n(e)]$ . For example,  $\beta_3(e) = m_1'(e)$ . Hence,  $\|\beta_3(C)\| = \|m_1'(C)\| = \sum_{e \in C} m_1'(e)$  (Figure 3.6.C). Therefore, Equation 3.11 can be formulated as:

(3.12) a) minimize:

$$Q(C) = F(\|\beta_1(C)\|, \|\beta_2(C)\|, \|\beta_5(C)\|)$$

b) constraints:  $\|\beta_3(C)\| \le \beta_3^{\max}$  and  $\|\beta_4(C)\| \le \beta_4^{\max}$

The term  $\beta_3^{\text{max}}$  (and  $\beta_4^{\text{max}}$ ) denotes the same value we had in Equation 3.11, i.e., available memory of processor 1 (and 2).

**3.3.2.** Graph Expansion. The number of convex cuts C in G can grow exponentially with respect to graph complexity. In order to tractably find the optimal path, we would need to eliminate paths that are guaranteed to yield inferior solutions from consideration.

For this purpose, we first planarize the task graph G using the transformation developed in [HG09]. Note that although some programming languages, such as StreamIt [TKA02], guarantee task graph planarity, our proposed method does not require a specific language.

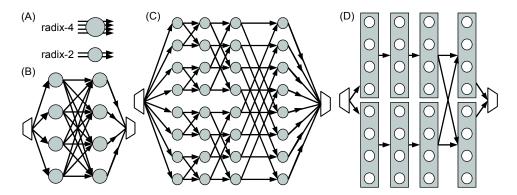

Given a planar embedding of G(V, E), we construct the well-defined dual graph  $G^*(V^*, E^*)$ . The  $\beta$  attributes of edges  $e \in E$  are transferred to the corresponding edges  $e^* \in E^*$  (Figure 3.6.D). A simple path  $P^*$  from vertex  $s^*$  to  $t^*$  in graph  $G^*$  identifies a convex cut C in graph G. Therefore, the dual graph enables us to evaluate the quality of a task assignment by evaluating the quality of the corresponding path from  $s^*$  to  $t^*$  in  $G^*$ . That is, since  $\|\beta_i(C)\| = \sum_{e \in C} \beta_i(e) = \sum_{e^* \in P^*} \beta_i(e^*) = \|\beta_i(P^*)\|$ , we evaluate Equation 3.12 from  $P^*$  instead

FIGURE 3.6. A) Task graph G(a, f) and a sample cut C. B) New attributes after the transformation. C) Vector representation of the attributes. D) Dual graph  $G^*(s^*, t^*)$ , and path  $P^*$ .

of C:

(3.13) a) minimize:

$$Q(P^*) = F(\|\beta_1(P^*)\|, \|\beta_2(P^*)\|, \|\beta_5(P^*)\|)$$

b) constraints:  $\|\beta_3(P^*)\| \le \beta_3^{\max}$  and  $\|\beta_4(P^*)\| \le \beta_4^{\max}$

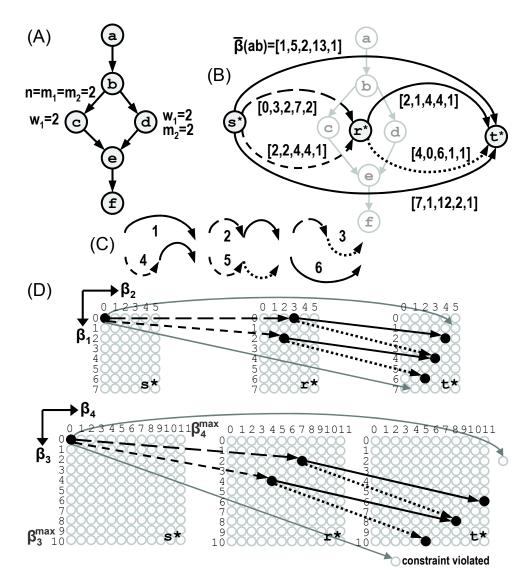

Next, we expand the dual graph  $G^*$  to a graph  $G^{\dagger}$ , constructed in four dimensional (4-D) space, to better visualize the situation (Figure 3.7). Each dimension of  $G^{\dagger}$  represents one element of the attribute vector, e.g., workload of the top partition. For every vertex  $v^*$  in  $G^*$ , we have vertices  $v^*[i_1, i_2, i_3, i_4]$  in graph  $G^{\dagger}$  in 4-D space. For example in the figure, vertex  $r^*$  is expanded into two vertices  $r^*[0, 3, 2, 7]$  and  $r^*[2, 2, 4, 4]$  (4-D indices of the two vertices are in the middle column of Figure 3.7.D). Graph  $G^{\dagger}$  is constructed such that the information stored in  $\vec{\beta}(e^*)$  attributes in graph  $G^*$ , is represented in the structure of graph  $G^{\dagger}$ . Formally, vertex  $u^*[\vec{i}]$  (abbreviation for  $u^*[i_1, i_2, i_3, i_4]$ ) is connected to vertex  $v^*[\vec{j}]$  in

FIGURE 3.7. A) In task graph G(a, f), all the attributes  $w_1, w_2, n, m_1$  and  $m_2$  are equal to 1, except for those shown in the figure. B) Dual graph  $G^*(s^*, t^*)$  and the  $\vec{\beta}$  attributes. C) Six possible paths to choose from. D) Construction of  $G^{\dagger}$  in 4-D space.

$G^{\dagger}$  when:

(3.14)

$$\begin{cases} \text{there exists an edge } e^*(u^*, v^*) \text{ in } G^* \\ \text{and } \vec{i} + \vec{\beta}(e^*) = \vec{j} \end{cases}$$

where only the first four elements of  $\vec{\beta}$  is used in this equation. In other words, for a given edge  $e^*$  connecting  $u^*$  to  $v^*$  in graph  $G^*$  and a given vector  $\vec{i}$ , there is a unique edge in  $G^{\dagger}$  which connects vertex  $u^*[\vec{i}]$  to  $v^*[i+\vec{\beta}(e^*)]$ . As a result, for a given path  $P^*$  from  $s^*$  to  $t^*$  in  $G^*$ , and a given start vector  $\vec{o}$ , there is a unique path in  $G^{\dagger}$  starting from  $s^*[\vec{o}]$ .

That is,  $\beta_5(u^*[\vec{i}], v^*[\vec{j}]) = \beta_5(u^*, v^*)$ . Moreover, if we choose  $\vec{o} = [0, 0, 0, 0]$ , the path in  $G^{\dagger}$  always ends at  $t^*[\vec{\beta}(P^*)]$ , because each edge from  $u^*[\vec{i}]$  to  $v^*[\vec{j}]$  in the path incurs an increase of  $\vec{j} - \vec{i}$  in the value of  $\vec{\beta}(P^*)$ . In graph  $G^{\dagger}$ , graph structure replaces the attribute information except for  $\beta_5$ , which annotates the edges of  $G^{\dagger}$  in the same way as edges of  $G^*$ . For example, consider cut  $C_4 = \{ce, bd\}$  or equivalently  $P_4^* = \{\text{dash, black}\}$ . Using graph  $G^*$  (Figure 3.7.A), we calculate  $\vec{\beta}(P_4^*)$  as [2, 2, 4, 4, 1] + [2, 1, 4, 4, 1] = [4, 3, 8, 8, 2], while in graph  $G^{\dagger}$  we have the same value (the first four elements of the vector) by simply looking up the index of  $t^*$  at the end of path  $P_4^*$  (Figure 3.7.D).

Therefore, one can evaluate Equation 3.13 for all possible paths by enumerating the vertices  $t^*$  at the end of every path  $P^*$  in graph  $G^{\dagger}$ . Let us denote the end point as  $\tilde{t}(P^*)$ . For example,  $\tilde{t}(P_4^*) = [4, 3, 8, 8]$ , because  $P_4^*$  ends at vertex  $t^*[4, 3, 8, 8]$ . The problem can be reformulated as:

(3.15)

$$a) \text{ minimize:} \quad Q(P^*) = F(\tilde{t}_1(P^*), \tilde{t}_2(P^*), ||\beta_5(P^*)||)$$

$$b) \text{ constraints:} \quad \tilde{t}_3(P^*) \le \beta_3^{\text{max}} \text{ and } \tilde{t}_4(P^*) \le \beta_4^{\text{max}}$$

Note that constructing of  $G^{\dagger}$  does not reduce algorithmic complexity of the partitioning. It is merely outlined for better visualization, and to enable subsequent optimizations.

3.3.3. Hard Constraints. A path in  $G^{\dagger}$  that visits the vertex  $v[\vec{i}]$  will lead to a partitioning solution whose first four attributes are at least as large as the elements of i. Therefore, we can trim out infeasible solutions, violating at least one of the hard constraints, during construction of  $G^{\dagger}$ . This is achieved not by trimming paths that violate Equation 3.15.b after construction of  $G^{\dagger}$ , but by refusing to insert violating edges in  $G^{\dagger}$  in the first place. Each time we are about to connect an existing vertex  $u^*[\vec{i}]$  to a new vertex  $v^*[\vec{j}]$ , violations of the hard constraints can be detected, in which case, vertex v and the edge are discarded. For example in Figure 3.7, assume  $\beta_3^{\max} = 10$  and  $\beta_4^{\max} = 11$ . Path  $P_1^*$  violates the constraint because  $0 + \beta_4(ab) \ge \beta_4^{\max}$ , i.e., the 4th attribute of the new vertex  $t^*[1,5,2,\underline{13}]$  is beyond the limit.  $P_6^*$  violates the constraint too. Thus, vertex  $u^*[\vec{i}]$  is connected to vertex  $v^*[\vec{j}]$  only if:

(3.16)

$$\begin{cases} \text{there exists an edge } e^*(u^*, v^*) \text{ in } G^* \\ \text{and } \vec{i} + \vec{\beta}(e^*) = \vec{j} \\ \text{and } j_3 \leq \beta_3^{\text{max}} \text{ and } j_4 \leq \beta_4^{\text{max}} \end{cases}$$

As a result, graph  $G^{\dagger}$  is constructed such that any path from s\* to a  $t^*$  vertex in  $G^{\dagger}$  identifies a feasible solution. It follows that Equation 3.15.b can be removed from consideration, and fewer paths that are left in  $G^{\dagger}$  should be evaluated to optimize Equation 3.15.a.

Other constraints can be encoded similarly. For example, one could embed hard constraints on the maximum workload that could be assigned to either processor, which translates to trimming edges in  $G^{\dagger}$  based on the first or second attribute.

**3.3.4.** Cost Function Minimization. The first four elements in the attribute vector of a path from  $s^*[\vec{0}]$  to  $\tilde{t}$  can be expressed based on the coordinates of the  $\tilde{t}$  vertex in 4-D space. Hence, all paths that terminate at the same end point in  $G^{\dagger}$  share the same attribute vector. That is, all such paths lead to task assignments that incur the same workload and memory distribution, and are only different in their inter-processor communication volume.

Among such possible task assignments, one would typically prefer the solution that incurs the minimum communication. This is to say that the cost function Q is non-descending in the fifth element of the attribute vector, i.e.,  $\|\beta_5(P^*)\|$ . Equivalently, among a group of competing paths terminating at the same end point, we are interested in the path with minimum  $\beta_5$ .

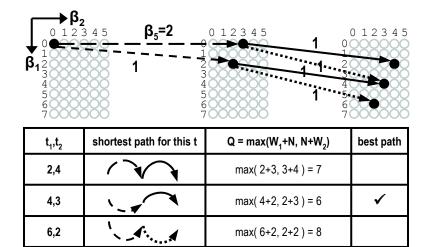

Recall that the edges of  $G^{\dagger}$  are annotated with their  $\beta_5$  attribute. We can treat edge annotations as distance labels in  $G^{\dagger}$ , and run single-source multiple-destination shortest path on the graph from source vertex  $s^*[\vec{0}]$  to all possible  $\tilde{t}$  end points. The shortest path procedure would prune many possible paths that do not minimize cost function Q. Specifically, for every possible end point  $\tilde{t}$ , it only leaves one path in the graph that terminates there. For example in Figure 3.7.D, two paths arrive at the same end point:  $\tilde{t}(P_3^*) = \tilde{t}(P_4^*) = [4, 3, 8, 8]$ . However, only  $P_4^*$  is maintained for end point  $t^*[4, 3, 8, 8]$  (Figure 3.8).

FIGURE 3.8. Finding the shortest paths to  $t^*$  end points, and evaluating the cost function  $Q = \max\{\|w_1(V_1)\| + \|n(c)\|, \|w_2(V_2)\| + \|n(c)\|\}$  for them.

We can calculate the value of Q at each of the  $\tilde{t}$  points to find the end point, and the corresponding path, which globally minimizes Q (Figure 3.8). This procedure delivers an exact solution, which is guaranteed to optimize the cost function subject to hard constraints.

One might be able to prune out more candidate points from consideration, if more specific information about the cost function is known. For example, if one wants to avoid highly skewed workload distribution, he can ignore the end points whose  $w_1$  or  $w_2$  attribute is below or above a certain threshold.

**3.3.5.** Algorithm Complexity. The task graph and subsequent graphs constructed from that are directed acyclic graphs. Hence, the complexity of discussed transformations and the shortest path algorithm grow linearly with the number of edges in the subject graphs. Note that on a DAG, single source shortest path can be implemented using topological sort and thus has linear complexity [CLRS01a].

In planar graphs, the number of edges grows linearly with the number of vertices. Therefore, time complexity of our algorithm is determined by the number of vertices in the largest subject graph, i.e.,  $G^{\dagger}$ . There are at most  $|V| \times \beta_1^{\max} \times \beta_2^{\max} \times \beta_3^{\max} \times \beta_4^{\max}$  vertices in  $G^{\dagger}$ , where |V| is the number of vertices in the application task graph. Thus, our algorithm has the time complexity of  $O(|V| \times \prod_{i=1}^4 \beta_i^{\max})$ .

This is considered pseudo-polynomial because the terms  $\beta_i^{\text{max}}$  merely depend on the properties of the application graph and target platform.  $\beta_3^{\text{max}}$  and  $\beta_4^{\text{max}}$  represent the

available memory on the processors. Moreover,  $\beta_1^{\max}$  is independent of the path choice, because  $\|\beta_1(P^*)\| = \|\beta_1(C)\| = \sum_{v \in G_1} w_1(v)$  and thus its maximum value,  $\beta_1^{\max}$ , is the computation workload of the entire application when all tasks are assigned to processor 1. A similar argument holds for  $\beta_2^{\max}$ .

Note that since our graph bi-partitioning problem is NP-Complete no algorithm with strictly-polynomial complexity exists unless P = NP. The pseudo-polynomial complexity does not impose a real constraint on practicality of our approach. Pseudo-polynomial time algorithms incur reasonable latency for typical problem instances, unless we have to deal with very large attribute numbers which are uncommon in many practical settings [GJ90]. In practice, the attributes can be normalized so that  $\beta_i^{\text{max}}$  values remain relatively small.

### 3.4. Approximation Method

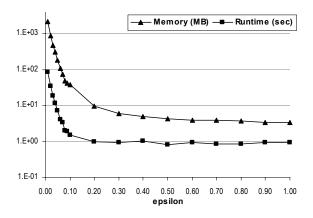

In this section, we present an approximation method for our exact task assignment algorithm with strictly-polynomial complexity. The approximation algorithm takes as input an acceptable error bound  $\xi$ , e.g., 10%, and guarantees that quality, i.e., throughput, of the near-optimal solution would not be more than a factor of  $\xi$  away from the optimal throughput.

We reduce the complexity by simplifying graph  $G^{\dagger}$  in the exact algorithm. We illustrate that partitioning quality is not degraded beyond the intended limit in the course of the process. Specifically, the number of vertices in the expanded graph  $G^{\dagger}$  is reduced to  $O(|V| \times \Pi_{i=1}^4 \log \beta_i^{\max})$  from the original  $O(|V| \times \Pi_{i=1}^4 \beta_i^{\max})$ . In each of the four  $\beta_i$  dimensions of the 4-D space in  $G^{\dagger}$ , we judiciously trim the  $\beta_i^{\max}$  possible values of indices to only  $\log \beta_i^{\max}$  distinct numbers.

The idea is to replace multiple attribute values with a single representative value for that attribute. That is, we would like to develop an approximation function  $\ddot{\beta} = f(\beta)$  to generate a representative value  $\ddot{\beta}$  for a range of  $\beta$  values. For a given number  $\delta > 0$ , the approximation function is defined as

(3.17)

$$\ddot{\beta} = f(\beta) = (1+\delta)^{\left\lfloor \log_{1+\delta}^{\beta} \right\rfloor} \text{ and } f(0) = 0$$

We apply this function whenever a new edge is to be added to graph  $G^{\dagger}$ . Thus, for constructing the path corresponding to  $P^*$  from  $s^*$  to  $t^*$  in  $G^*$ , the approximation function

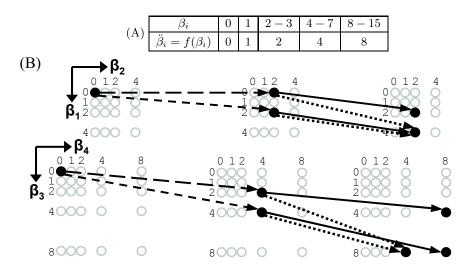

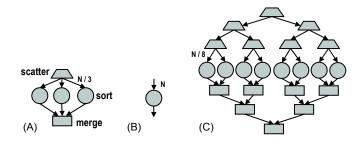

FIGURE 3.9. A) Approximation function. B) Constructing the approximated graph  $G^{\dagger}$  from Figure 3.7.

is applied k times, where k is the number of edges in path  $P^*$ . Figure 3.9 illustrates the idea when  $\delta = \vec{1}$ , and possible values are trimmed to only 0, 1, 2, 4, and 8.

For example, consider path  $P_3^* = \{\text{longdash}, \text{dot}\}$  in Figure 3.9. Originally, the longdash-marked edge connected  $s^*[0,0,0,0]$  to  $r^*[0+0,0+3,0+2,0+7] = r^*[0,3,2,7]$ . After applying the approximation, the path ends at  $r^*[f(0+0),f(0+3),f(0+2),f(0+7)] = r^*[0,2,2,4]$ . Similar procedure is applied to the next edge in the path, i.e., the dot-marked edge. It starts from the approximated vertex  $r^*[0,2,2,4]$  and ends in  $t^*[f(0+4),f(2+0),f(2+6),f(4+1)] = t^*[4,2,8,4]$ .

After approximation, the number of vertices in the graph  $G^{\dagger}$  becomes proportional to  $|V| \times \Pi_{i=1}^4 \log \beta_i^{\max}$ , because in each of the four  $\beta_i$  dimensions, the above approximation function results in one of the following possible distinct numbers:  $0, 1, 1+\delta, (1+\delta)^2, \cdots, (1+\delta)^b$ , where  $b = \lfloor \log_{1+\delta}^{\beta_i^{\max}} \rfloor$ .

LEMMA 3.5. We have

$$\frac{\beta}{1+\delta} < \ddot{\beta} \le \beta$$

THEOREM 3.6. If we set  $\delta = \sqrt[F]{1+\epsilon} - 1$ , where  $\epsilon > 0$  and F is the number of faces in task graph G, then we have

(3.18)

$$\frac{\|\beta(P^*)\|}{1+\epsilon} < \|\ddot{\beta}(P^*)\| \le \|\beta(P^*)\|$$

This means that for every path  $P^*$  from  $s^*$  to  $t^*$  in the expanded graph  $G^{\dagger}$ , the approximated value  $\|\ddot{\beta}(P^*)\|$  is at most degraded by a factor of  $1 + \epsilon$  from its original value  $\|\beta(P^*)\|$ .

Note that  $\beta$  and  $\ddot{\beta}$  are vectors. In fact,  $\delta$  is also a vector with four elements, which implies that we can have different approximation factors for different dimensions of the 4-D space. All mathematical operations are performed on each of the four dimensions independently.

The following theorems quantify the impact of approximation on memory constraints and cost function minimization.

Corollary 3.7. The original hard constraints

(3.19)

$$\|\beta_3(P^*)\| \le \beta_3^{\max} \text{ and } \|\beta_4(P^*)\| \le \beta_4^{\max}$$

can be replaced with following constraints, which use approximated values

(3.20)

$$\|\ddot{\beta}_3(P^*)\| \le \frac{\beta_3^{\max}}{1+\epsilon} \text{ and } \|\ddot{\beta}_4(P^*)\| \le \frac{\beta_4^{\max}}{1+\epsilon}$$

Corollary 3.8. Let  $\ddot{\beta}^{\max} = f(\beta^{\max})$ . The constraints

(3.21)

$$\|\ddot{\beta}_3(P^*)\| \le \ddot{\beta}_3^{\max} \text{ and } \|\ddot{\beta}_4(P^*)\| \le \ddot{\beta}_4^{\max}$$

guarantee that

(3.22)

$$\|\beta_3(P^*)\| \le (1+\epsilon)\beta_3^{\max} \text{ and } \|\beta_4(P^*)\| \le (1+\epsilon)\beta_4^{\max}$$

Therefore, to construct the new set of memory constraints, we may use either of the above two corollaries. The formula in Corollary 3.7 guarantees that the original constraints are met, at the expense of trimming some possibly-valid paths. The formula in Corollary 3.8 provides a new constant bound within a factor of  $1 + \epsilon$  from the bound in the original constraint. We proceed to consider the impact of approximation on cost function minimization.

THEOREM 3.9. Let  $\ddot{Q}(P^*) = F(\|\ddot{\beta}_1(P^*)\|, \|\ddot{\beta}_2(P^*)\|, \|\beta_5(P^*)\|)$  denote the approximated value of our cost function  $Q(P^*) = F(\|\beta_1(P^*)\|, \|\beta_2(P^*)\|, \|\beta_5(P^*)\|)$ , for the path  $P^*$ . We

have

$$(3.23) (1 - \frac{\epsilon}{1 + \epsilon} S(P^*)) Q(P^*) \leq \ddot{Q}(P^*) \leq Q(P^*)$$

where  $S(P^*)$  is defined as

(3.24)

$$S(P^*) = \frac{\|\beta_1(P^*)\|}{Q(P^*)} \max \frac{\partial Q}{\partial \beta_1} + \frac{\|\beta_2(P^*)\|}{Q(P^*)} \max \frac{\partial Q}{\partial \beta_2}$$

Note that although Q is originally a discrete function, throughout the following mathematical analysis, we look at it as a continuous function. That is, we use the same formula for Q, but assume its domain is  $\mathbb{R}$  instead of  $\mathbb{N}$ . Note that Q does not have to be differentiable. As long as Q is differentiable on several intervals and continuous (i.e., piece-wise differentiable), we are able to calculate the maximum slope. For example,  $\max \frac{\partial Q}{\partial \beta_1} = \max \frac{\partial Q}{\partial \beta_1} = 1$  for  $Q = \max\{\|w_1(V_1)\| + \alpha_1\|n(c)\|, \alpha_2\|n(c)\| + \|w_2(V_2)\|\} = \max\{\|\beta_1(C)\| + \alpha_1\|\beta_5(C)\|, \alpha_2\|\beta_5(C)\| + \|\beta_2(C)\|\}$ , because the slope of Q with respect to both  $\|\beta_1(C)\|$  and  $\|\beta_2(C)\|$  is either 0 or 1 on its entire domain.

Corollary 3.10. Let  $S^{\max}$  be the maximum possible value of S over the domain of function Q. We have

$$(3.25) \qquad \forall P^*: \left(1 - \frac{\epsilon}{1 + \epsilon} S^{\max}\right) \, Q(P^*) \le \ddot{Q}(P^*) \le Q(P^*)$$

The above theorem states that the error in calculating cost function is bounded within a constant factor. The main objective of graph bi-partitioning is to find the optimal path  $P^* = P_{opt}^*$  which minimizes our cost function  $Q(P^*)$ . Using the approximation method, however,  $\ddot{Q}(P^*)$  is minimized for some near-optimum path  $P^* = P_{near}^*$ .

COROLLARY 3.11. Let

$$\xi = \frac{\epsilon}{1+\epsilon} S^{\max}$$

, and  $T = \frac{1}{Q}$  denote the throughput. We have

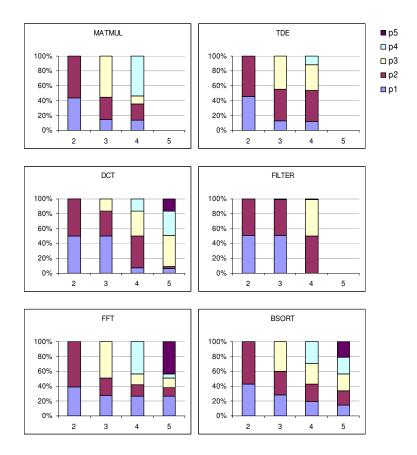

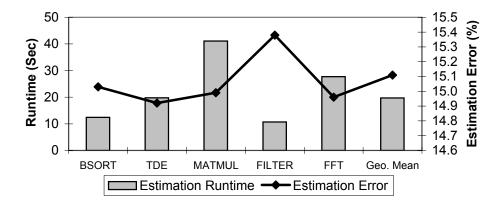

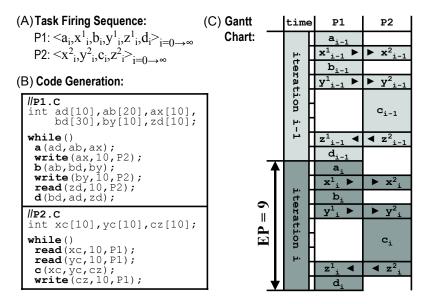

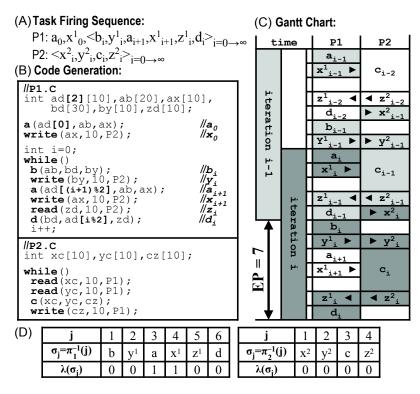

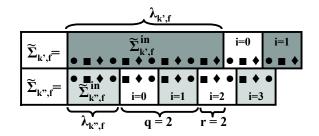

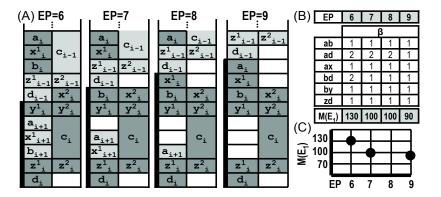

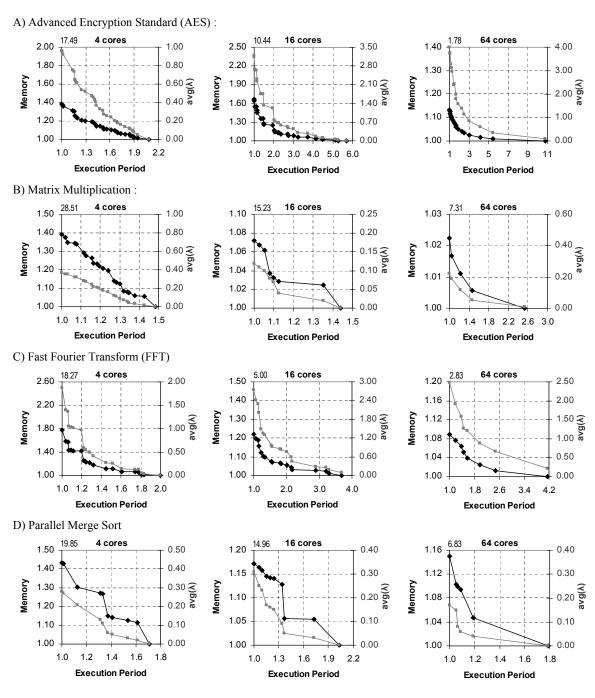

$$(3.26) \qquad (1-\xi) T_{out} \leq T_{near} \leq T_{out}$$