# Advances in Streaming Software Synthesis for Manycore Processor Platforms

By

Mohammad H. Foroozannejad

B.S. (Shahid Beheshti University) 2001

# DISSERTATION

Submitted in partial satisfaction of the requirements for the degree of

# DOCTOR OF PHILOSOPHY

in

ELECTRICAL AND COMPUTER ENGINEERING

in the

OFFICE OF GRADUATE STUDIES

of the

UNIVERSITY OF CALIFORNIA

DAVIS

Approved:

Soheil Ghiasi, Chair

Venkatesh Akella

Bevan Baas

Committee in Charge

2015

#### Abstract

Continuation of Moore's law and advances in fabrication technologies have enabled development of digital computing platforms that contain many processor cores. Such chip multiprocessor (CMP) architectures exhibit significant promise in energy and throughput sensitive applications, while offering the flexibility of software programmability. However, development of scalable parallel software for utilization of such CMP platforms remains a major challenge. As the trend in CMP design points to placing of more processor cores on the chip, the programming challenge is only going to be exacerbated in the future.

This PhD research takes several strides toward addressing the problem of parallel soft-ware development for a specific class of embedded applications. In particular, we focus on automated synthesis of parallel software for streaming applications that are to be executed on distributed-memory CMP platforms. Streaming applications demand processing of a seemingly endless stream of input data, as they are presented to the system. Typically, processing at any point demands access to a small window of input data, hence the output can be computed and streamed out as the input flows into the system. Such applications are abundant in the embedded systems space. Examples include various signal processing, data encoding/decoding schemes, multi-media, security and network inspection applications.

We advocate productive development of streaming applications by synthesizing software from high-level specifications, such as data flow graphs. In this context, we first study the problem of inter-actor buffer allocation during software synthesis from synchronous dataflow models. Buffer allocation strategy greatly impacts the memory footprint of the synthesized streaming software, which is critical for memory-constrained embedded CMPs. Next, we discuss the problem of mapping virtual processors onto physical processors of a GALS-based manycore platform, and present a constructive optimization approach that offers a controllable tradeoff between mapping quality and compilation runtime. Finally, we identify redundant memory access as a critical performance bottleneck in automatically generated streaming software. We develop a memory access analysis and optimization technique for streaming applications, which exploits properties of synchronous dataflow models to improve performance of the synthesized code.

## Acknowledgments

I would like to express my special appreciation and thanks to my esteemed teachers and mentors especially my advisor Professor Soheil Ghiasi, who has been a tremendous mentor for me. I would like to thank him for all his encouragement and for helping me to grow as a research scientist. His advice on both research as well as on my career have been priceless. I would like to thank my committee members, Professor Bevan Baas and Professor Venkatesh Akella for their brilliant comments and suggestions. I would also like to extend a special thanks to the UC Davis faculty for teaching informative courses and the ECE department staff for their support.

A special thanks goes to my family; words cannot express how grateful I am to my mother and father for all of their support and sacrifice. Their prayers for me sustained me thus far. At the end I would like to express my appreciation to my dearest wife Sahbanoo who selflessly cherished our beloved children during my research. She always supported me in the moments when there was no one else by my side.

I am deeply indebted to Matin Hashemi, Trevor L. Hodges, Alireza Mahini, Mohammad Motamedi, and Brent Bohnenstiehl for their assistance.

# Contents

| Abstract                                                               | ii  |

|------------------------------------------------------------------------|-----|

| Acknowledgments                                                        | iii |

| Chapter 1. Introduction                                                | 1   |

| Chapter 2. Background                                                  | 5   |

| 2.1. Manycore Platforms                                                | 5   |

| 2.2. Synchronous Data Flow Models                                      | 6   |

| 2.3. Software Synthesis                                                | 8   |

| Chapter 3. Post-Scheduling Buffer Allocation                           | 11  |

| 3.1. Buffer Memory Management                                          | 12  |

| 3.2. Granularity in Buffer Analysis                                    | 16  |

| 3.3. Buffer Allocation Problem                                         | 22  |

| 3.4. ILP Formulation                                                   | 23  |

| 3.5. Strip Packing Problem and Buffer-Sharing                          | 26  |

| 3.6. Evolutionary Buffer Optimization                                  | 27  |

| 3.7. Extension of The Reference Model                                  | 33  |

| 3.8. Complexity vs. Optimality                                         | 39  |

| 3.9. Experimental Evaluation                                           | 41  |

| Chapter 4. Processor Mapping for Circuit-Switched GALS-Based Manycores | 49  |

| 4.1. Target Platform and Application Model                             | 50  |

| 4.2. Problem Statement                                                 | 52  |

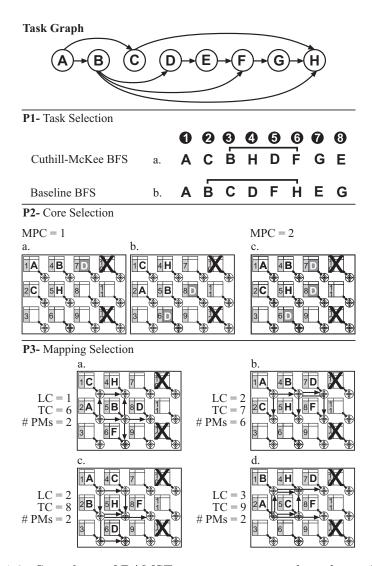

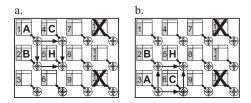

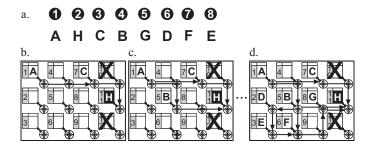

| 4.3. BAMSE Algorithm                                                   | 54  |

| 4.4. Complexity vs. Quality                                            | 63  |

| 4.5. Experimental Evaluation                                           | 66  |

| Chapter 5. Memory Access Analysis and Optimization | 77  |

|----------------------------------------------------|-----|

| 5.1. Motivating Example                            | 78  |

| 5.2. Problem Statement                             | 79  |

| 5.3. Memory Access Modeling                        | 79  |

| 5.4. RACE Algorithm                                | 86  |

| 5.5. Extensions to RACE                            | 93  |

| 5.6. Experimental Evaluation                       | 96  |

| Chapter 6. Related Work                            | 105 |

| Chapter 7. Conclusion and Future Work              | 110 |

| Bibliography                                       | 115 |

#### CHAPTER 1

# Introduction

For several years, advances in silicon technology has increased computing performance via enhancing clock frequency and employing more silicon budget. Nonetheless, increasing performance through maximizing clock speed does not seem to as efficient anymore as it appears to have been pushed to its limit [Bor99]. Moreover, the popularity of the hand-held devices in recent years with limited battery life has made energy efficiency an important factor in computing systems. On the other hand, it is well-known that we can achieve performance using parallelism in an energy efficient way [CSB92]. To remedy the power consumption limitations and still be able to achieve performance simultaneously, Chip Multiprocessor (CMP) platforms have been used for research purposes as well as the commercial marketplace [ABC<sup>+</sup>06].

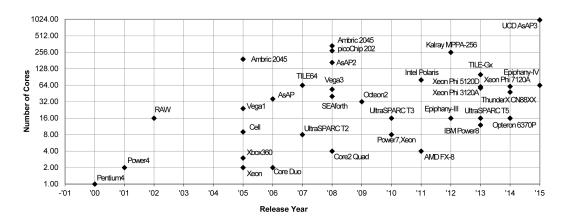

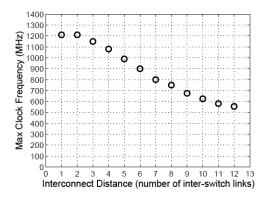

Current technology trends suggest that integrating more processor cores per chip will continue, and domain-specific **manycore** chips with 1000+ cores seem imminent [ABD<sup>+</sup>09, V<sup>+</sup>07, TCM<sup>+</sup>09]. Figure 1.1 is an extended version of the data reported in [Has11] and shows the current trend in many-core technology. Distributed-memory CMPs are arguably most appropriate for massive parallel computing systems due to scalability of their memory architecture and their message passing-based programming model. Such platforms, e.g. the Asynchronous Array of Simple Processors (AsAP) [TCM<sup>+</sup>09], are well-positioned to specifically benefit embedded systems with data-intensive applications.

A significant group of embedded applications are characterized by their requirement to process a steady stream of input data as they are presented to the system. Such applications, which are generally referred to as streaming applications, demand access to merely a small window of input data at each point in time. Thus, output can be produced and streamed out, possibly with a time lag, as the input flows into the system. Streaming applications emerge in different disciplines, such as encoding, decoding, transformation and inspection protocols in multi-media, signal processing, security, and networking domains.

FIGURE 1.1. Current trend in many-core processors. The data shown in this Figure is an extended version of the data reported in [Has11]

Most streaming applications either have fixed-rate behavior, or contain fixed-rate kernels at their heart [GB04]. Synchronous Data Flow (SDF) graphs [LM87b] and their variations, such as Cyclo-Static data flow graphs [BELP95], are widely used to model fixed-rate applications. In these models, the processing is captured by a number of tasks that communicate solely via point-to-point channels. The channels deliver the data to the receiver in the same order that they are generated by the producer. Because of abundant parallelism and predictable data patterns, they are suitable for being efficiently executed on CMP platforms.

The intensity of the computation and communication among parallel processing units makes it very hard for the programmer to flawlessly implement the target function while paying attention to the various details of the system. On the other hand, productive parallel systems have shown sensitive to the implementation details [ABD+09]. In fact, a poorly-written parallel code may cause low performance compared to its equivalent sequential code while consuming more resources. Automated software synthesis significantly reduces the development and debugging time, providing portability of the generated function. The idea is to enable seamless and efficient transformation from a higher-order specification of the application to parallel software code for a given target parallel system, such as ones in manycore processor platforms. One of the main objectives of software synthesis is to maximize throughput, which is an important quality metric in the streaming application

domain. However, there can be other optimization objectives and/or constraints such as judicious use of memory and communication resources on chip which are imposed by resource availability of the target hardware platform.

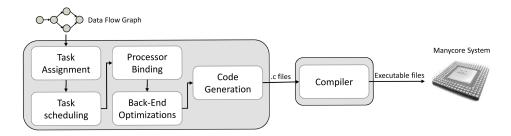

An automated software synthesis process consists of several key algorithmic steps including task assignment, task scheduling, buffer allocation, processor mapping, and code generation. In Chapter 2.1, we will describe the flow of the software synthesis process with a brief explanation of each algorithmic step. We also present an overview of the abstraction models we use for manycore platforms and also streaming applications throughout this dissertation.

The major contribution of this dissertation is presented in Chapters 3 through 5. Chapter 3 contributes to the backend optimization step of the automatic software synthesis flow. In this Chapter, we study the inherent tradeoff between memory requirement and compilation runtime, under a given task firing schedule in the context of streaming software synthesis from data flow graphs. We utilize post-scheduling analysis granularity to control the amount of details in characterization of buffers spatio-temporal footprints. Subsequently, we transform the buffer allocation problem to two dimensional packing of polygons, where complexity of the packing problem (e.g., polygon shapes) is determined by the analysis granularity. We develop an evolutionary packing optimization algorithm, which readily yields buffer allocations. Experimental results highlight the tradeoff between complexity of the analysis and the total buffer size of generated implementations. In addition, they show dramatic improvements in total buffer size, if one is willing to pay the additional cost in optimization runtime.

In Chapter 4, we study the problem of mapping concurrent tasks of an application to cores of a chip multiprocessor that utilize circuit-switched interconnect and Global Asynchronous Local Synchronous (GALS) [Cha84] clocking domains. We propose a mapping algorithm called BAMSE that exploits specific characteristics of such systems. The mapping quality affects application throughput, energy consumption, and even feasibility of implementing the application. BAMSE can strike a balance between mapping quality and optimization run time, as it explores the space of mapping solutions. Thus, BAMSE is useful in both compile time and run time application mapping. The proposed technique naturally handles a number of practical requirements, such as architectural features of the

target platform, core failures, and hardware accelerators, and in addition, is scalable to a large number of tasks and cores.

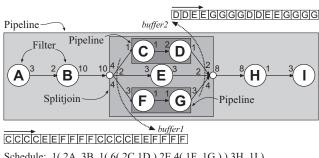

Chapter 5 takes the discussion on automated software synthesis beyond code generation. The software synthesis process typically implements inter-actor communication in form of buffer arrays that are written to/read from by producers/consumers (discussed in Chapter 3). Due to practical considerations (e.g., actor IPs) and the nature of SDF models, the generated code could contain a number of redundant buffer array accesses that become evident only in the synthesized software. In this Chapter, we identify the optimization opportunity and develop an algorithm called RACE, which optimizes the synthesized code via elimination of such redundant memory operations.

In Chapter 6 a flavor of the prior studies in the field are presented and discussed. Finally, in chapter 7 an overall summary of this dissertation is provided along with potential future avenues in the field.

#### CHAPTER 2

# Background

Right abstractions are the key to generating quality software in the embedded domain. In this Chapter, we present an overview of the two abstract models that we use throughout this dissertation. In Section 2.1, an abstract model for manycore platforms is presented, and in Section 2.2, SDF graphs are presented as the programming model for streaming applications. Section 2.3 presents the optimization steps involved in automated software synthesis from data flow models to manycore platforms.

#### 2.1. Manycore Platforms

Manycore processors can be represented as a graph in which, vertices model processing units (cores) and directed edges represent inter-core communication links. In this level of obstruction, the inter-core communication can be realized as FIFO channels where one core writes in and the other core reads from. The capacity of these channels represented as edge weights on the graph. Note that this is the abstract view of the hardware, and not necessarily the available physical hardware. For example, a shared-memory multi-core architecture can realize the abstract view by implementing inter-processor link in shared memory. In such architectures, unidirectional FIFO channels are implemented as arrays in the shared memory space. The access to the array has to be synchronized via a conventional locking mechanism.

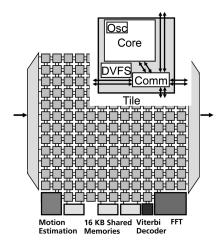

Circuit-switched GALS (Globally Asynchronous Locally Synchronous) architectures are a variation of Manycore platforms. AsAP2 [TCM+09] is an example of such architectures. In AsAP-like circuit-switched architectures, links are statically allocated between two communicating cores at the programming phase after reset when the application is loaded to the processor. Therefor, these links cannot be shared by other inter-core connections. This is in contrast to packet-switched networks in which, the physical resources can be shared. The interconnect distance between communicating processors in AsAP-like architectures have a reverse impact on the clock frequency of the source processor [TTB10], i.e., in

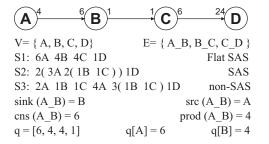

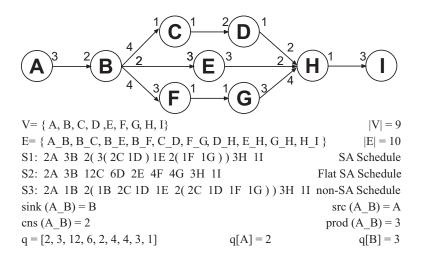

FIGURE 2.1. An example SDF graph, several valid schedules and some definitions are illustrated. SDF edges are annotated with corresponding production and consumption rates. V is the set of vertices and E is the set of edges of the SDF graph. S1, S2, and S3 are three different valid schedules for the given SDF graph. Src and sink of an edge are the sending and receiving actors of the edge, and prod and cns of an edge are the number of tokens produced and consumed on the edge, respectively. q is the repetition vector of the SDF containing all repetition factors of the actors in the graph. Each element of q shows how many times a specific actor should be fired in total in a valid schedule.

longer communications, the clock frequency of the source core is decreased. The drop in the source core frequency is due to the fact that the clock signal of the source core is sent along with the data to maintain communication synchrony [TTB10]. In Chapter 4, the Circuit-switched GALS architectures are discussed in more details.

## 2.2. Synchronous Data Flow Models

Synchronous Data Flow (SDF) graphs are widely used to model streaming applications. Let  $V_G$  and  $E_G$  denote the set of vertices and directed edges of the SDF graph G, respectively. Vertices of the SDF graph, also known as actors, model application tasks, and directed edges represent inter-task communication channels. Edge e starts from the actor src(e) (source), and ends at the actor snk(e) (sink). Figure 2.1 depicts an example.

Upon execution, each task consumes a fixed number of data items, also known as tokens, from each of its input channels. The consumed tokens are processed to generate output data, which is subsequently written to output channels of the task after completion of the execution. The generated output also has fixed rate. Equivalently, each edge e is annotated with two prod(e) and cns(e) numbers, which refer to the number of tokens produced by src(e) and consumed by sink(e) upon execution, respectively.

Application tasks can be executed only after there are enough tokens to consume on their incoming edges. The produced tokens after execution of a task might enable execution of other tasks. Execution of a task is also referred to as firing of the corresponding actor in the model. Note that execution of a task implies that enough tokens already existed at its inputs. The streaming assumption implies that there is a sufficiently-large number of tokens at the primary input, input from outside the model, to be processed.

Task can be executed in different orders, also known as task schedules. Due to production and consumption rates, task execution changes the storage requirement of the inter-actor channels. If repetitive execution of a fixed task schedule maintains the channels storage requirement bounded, the schedule can be utilized to synthesize an implementation at compile time. Such a schedule identifies one period of execution of the application, which is iteratively invoked to process the input stream.

It follows that a periodic task execution schedule has to meet two conditions: 1) actors can be fired only after there are enough tokens to consume on their incoming edges, 2) all of the generated tokens have to be consumed by the end of the period, to enable infinite repetition of the schedule using finite channel storage. It is well-known that realistic application SDF can be scheduled statically [LM87a].

Let vector q denote the number of repetition of actors in the periodic schedule. Without loss of generality, we assume q refers to the simplest such vectors, i.e., not all of its elements can be divided by an integer larger than 1. To guarantee that all produced tokens are consumed by the end of the period, any static schedule has to guarantee the following for all edges of the SDF:

$$q[src(e)] \times prod(e) = q[sink(e)] \times cns(e)$$

The vector q is unique for real-life streaming applications [LM87a]. Thus, the number of firings of actors in any static schedule is constant, although their ordering might differ in the period. In particular, "Single Appearance" (SA) schedule refers to the ordering, in which each actor appears exactly once. Figure 2.1 depicts an example SDF graph, along with several example schedules and notations.

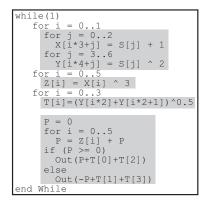

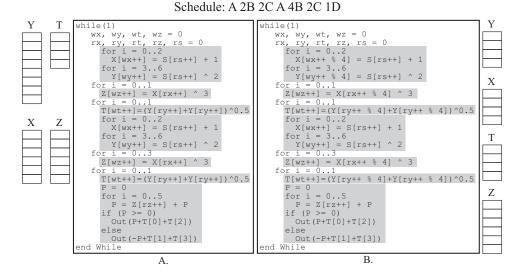

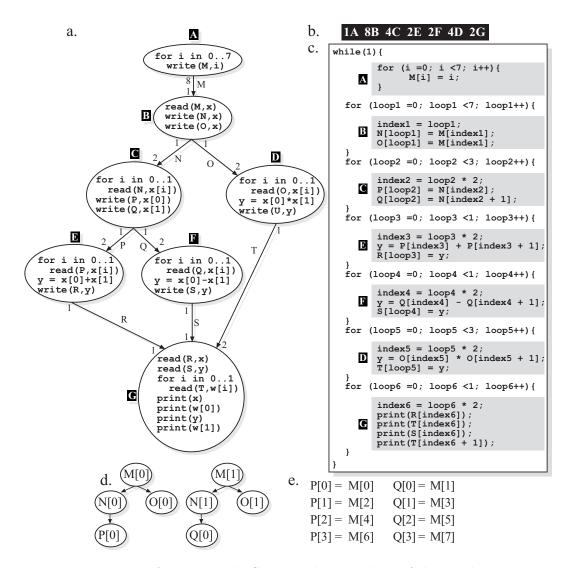

To synthesize software from a given SDF model, one needs to determine a periodic ordering for execution of the tasks, which can be infinitely repeated. In the baseline synthesis scheme, task v appears in a loop whose iteration count is q[v]. Subsequently, the loops are

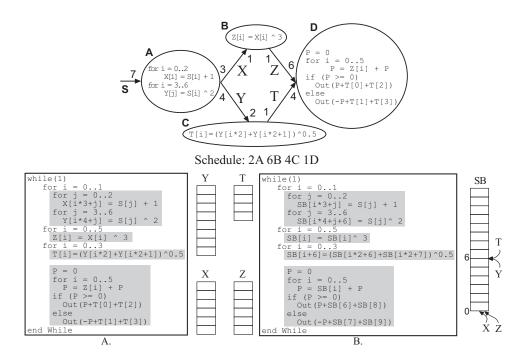

# Schedule: 2A 6B 4C D

FIGURE 2.2. An example SDF, and the corresponding baseline implementation. Channels are implemented as distinct buffers. V is the set of vertices and E is the set of edges of the task graph. S1, S2, and S3 are three different valid schedules for the given SDF graph. Src and sink of an edge are the sending and receiving nodes of the edge, and prod and cns of an edge are the number of tokens produced and consumed on the edge, respectively. q is the repetition vector of the SDF containing all repetition factors of the nodes of the graph. Each element of q shows how many times a specific actor should be fired in total in a valid schedule.

"stitched" together in the given order, with appropriate fixtures to implement inter-task communication. Figure 2.2 illustrates the synthesized code for the depicted SDF.

SA task scheduling enables the synthesizer to save in application code size by instantiating tasks' internal computations exactly once, possibly within nested loops. The code size overhead of looping constructs is negligible with respect to typical size of task internal computations. Therefore, SA schedules are widely used in embedded systems, since they lead to small size synthesized software. In this work, we assume the given schedule to be SA, unless otherwise noted.

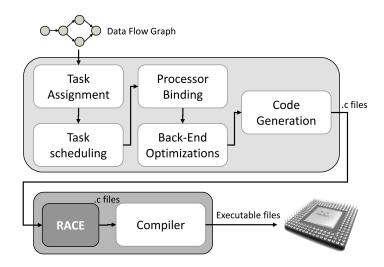

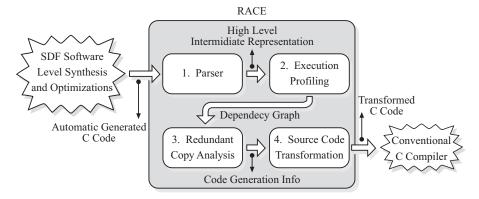

## 2.3. Software Synthesis

The software synthesis process involves several algorithmic steps, such as task assignment [HG10b, SK03], task scheduling [BLM96, MBL97], buffer allocation [MB04,

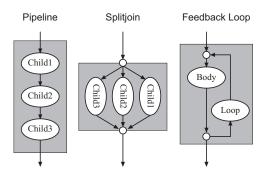

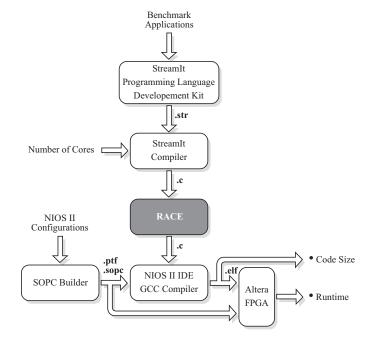

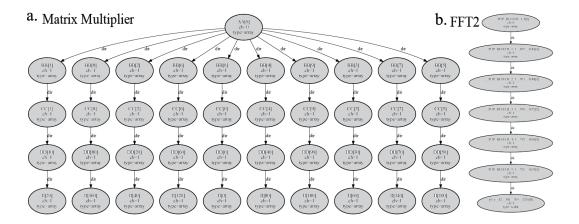

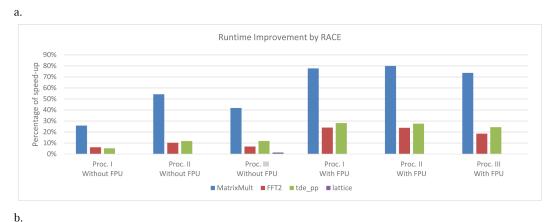

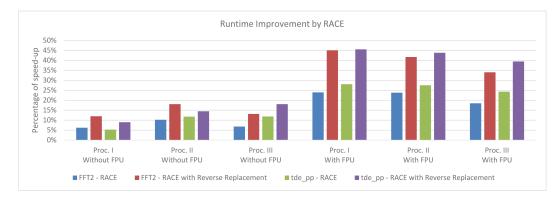

FIGURE 2.3. The flow of automatic software synthesis for SDF modeled streaming applications based on given application graph and target many-core model.

FHHG12], processor mapping [FHM<sup>+</sup>14, Tos11], and finally code generation [HRR91]. The combined effect of these algorithmic steps undertakes to produce high quality software from the SDF modeled application for the target hardware platform. Figure 2.3 demonstrates these steps in the order that they are performed in the synthesis process.

In the task assignment step, every task is assigned to a processor for execution. The typical objective of task assignment is to have a balanced workload among all processors and reduce inter processor communication at the same time. At this point, the processing units are considered to be virtual processors since the physical location of the processors on the chip is ignored [SK03].

After the task assignment step, each group of tasks that are assigned to a virtual processor will be executed on a uniprocessor. The order in which the tasks are executed sequentially on each core is calculated in the task scheduling step. Latency, code size, and data memory footprint are common objectives in this step. To this end, different types of algorithms have been introduced each of which has a different effect in terms of the given quality measures. Single Appearance (SA) scheduling is one of the scheduling methods which is commonly used in embedded platforms. In SA scheduling, each task appears only once in the sequential code, and hence yields the minimum code size.

Processor binding (processor mapping) allocates each virtual processor to a physical core on the chip. In this step, maximum and total communication distances between connecting cores are considered in addition to other network criteria such as dead-lock and congestion.

In the backend optimization step, post-scheduling and in-core resource allocation optimizations (e.g. buffer allocation) are performed [FHHG12].

Finally, in the code generation step of the synthesis process, the sequential code for each core is generated (usually in a high level programming language) [HRR91]. At this point, the modeled application has been completely converted to the sequential codes assigned to each core processor of the final hardware platform. The generated code can be passed to a standard compiler to generate executable binaries.

#### CHAPTER 3

# Post-Scheduling Buffer Allocation

In this Chapter, we study the inherent tradeoff between memory requirement and compilation runtime, under a given task firing schedule in the context of streaming software synthesis from data flow graphs. Due to the streaming nature of the applications, it is natural to realize the first-in-first-out (FIFO) channels as buffer arrays that are allocated as contiguous regions in the memory. In many streaming applications, buffers account for a substantial portion of the memory footprint of the synthesized programs [MB01, MB04]. The memory footprint of the synthesized application is especially critical when resource-constrained embedded platforms are targeted [HG10b].

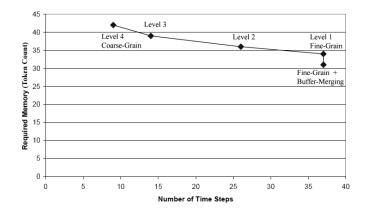

In this context, we study the problem of post-scheduling buffer management<sup>1</sup> during synthesis of embedded software from SDF models<sup>2</sup>. We show that the resolution in analysis of buffers' spatio-temporal behavior can serve as a control knob by which synthesizer runtime (complexity) can be traded off with total buffer size (quality). On one end of the spectrum, the least amount of analysis resolution approximates buffers' spatio-temporal behavior with conventional live ranges, while on the highest analysis resolution end, perturbations to buffers' characteristics after firing of every actor are taken into consideration. There are also other alternatives available between the two extreme cases.

We transform the buffer allocation problem into packing of complex polygons in the two dimensional time-space plane. The complexity of the polygons depends on the resolution level (granularity) of the analysis. We develop an evolutionary algorithm for the packing problem, which readily allocates buffers in the memory during compilation. The technique is implemented within the MIT StreamIt compiler [GTK<sup>+</sup>02], which compiles a specific variation of SDF. Experimental results on a number of streaming applications illustrate the tradeoff between optimization complexity and buffer size. Additionally, the empirical evaluation illustrates the superiority of our approach over existing competitors.

<sup>&</sup>lt;sup>1</sup>We use the term "buffer management" to refer to cost-benefit tradeoff in buffer allocation.

<sup>&</sup>lt;sup>2</sup>Please refer to Section 3.1 for an illustrative example and problem statement.

FIGURE 3.1. An example SDF graph, several valid schedules and some definitions are illustrated. Edges of the SDF graph are annotated with corresponding production and consumption rates. V is the set of vertices and E is the set of edges of the SDF graph. S1, S2, and S3 are three different valid schedules for the given SDF graph. Src and sink of an edge are the sending and receiving actors of the edge, and prod and cns of an edge are the number of tokens produced and consumed on the edge, respectively. q is the repetition vector of the SDF containing all repetition factors of the actors in the graph. Each element of q shows how many times a specific actor should be fired in total in a valid schedule.

## 3.1. Buffer Memory Management

Streaming applications tend to require fairly large channel buffers, primarily due to the data intensive nature of their processing and different production and consumption rates. As a result, the total size of the buffer arrays usually accounts for a substantial portion of the application binary memory footprint. Enhanced management of the buffer memory can potentially lead to considerable reduction in memory requirement, which would be of great value especially for the resource constrained embedded platforms.

In Section 2.2 of Chapter 2 we introduced the SDF graphs as the application model for streaming applications. Figure 3.1 shows an example of SDF graphs along with some of the main notations of the abstract model. We use this example to explain buffer sharing concepts in the reminder of this Chapter.

Recall that edge e in a SDF graph represents a FIFO communication channel between src(e) and sink(e). The channel stores the produced data after firings of src(e), and its data is consumed during firings of sink(e). Let MT(e, S) denote the maximum number of tokens stored in channel e during firing of tasks according to schedule S. Clearly, MT(e, S)

FIGURE 3.2. An example SDF, **A**. The corresponding baseline implementation. Channels are implemented as distinct buffers. **B**. Shared buffer implementation of the SDF.

indicates the minimum memory space required on this channel to implement the communication functionality.

The channels are typically implemented as buffer arrays to realize *in-order* communication with little cost. In the synthesized software, src(e) writes into the buffer that implements channel e by maintaining a write index, referred to as the Head. The Head is reset at the beginning of the period, and is incremented after writing every token. The initial resetting enables reusing the same buffer memory in subsequent iterations. Similarly, snk(e) maintains its own Tail index for reading from the buffer of channel e (buffer e for short), which is also reset at the beginning of the period, and is incremented after reading a token. Figure 3.2 illustrates the buffers in the synthesized code for the same example SDF given if Figure 2.2.

In presenting our work, we temporarily restrict our discussion to the aforementioned case of zero initial tokens on SDF edges, and single-appearance task execution schedule. We use the term "reference model" to refer to this case. Later in Section 3.7, we extend our discussions to demonstrate handling of both initial tokens, and non-single appearance schedules. We would like to emphasize that the temporary restriction of the discussion in

the next few Sections is merely for simplicity and clarity in presenting our work, and not a limitation of the proposed approach.

**3.1.1.** Baseline Buffer Allocation. Let MT(e, S) denote the maximum number of tokens stored in channel e during the firing of tasks according to schedule S. Clearly, MT(e, S) indicates the minimum memory space required on this channel to implement the communication functionality. Smaller buffer size would lead to an incorrect or infeasible execution under S, because at least at one point during execution MT(e, S) tokens need to be stored in the buffer e. In our discussions, therefore, we assume that the size of buffer e is exactly MT(e, S).

The baseline synthesis scheme would be to allocate the buffers as independent regions in the data memory. In the "baseline buffer allocation" scheme, the buffers do not share any physical memory location at any point during execution. It follows that the overall buffer size would be the sum total of individual buffers, i.e.,  $\sum_{e \in E} MT(e, S)$ . Figure 3.2.A depicts a simple example. If the schedule is clear from the context, we use  $MT_e$  to denote MT(e, S).

**3.1.2.** The Impact of Scheduling. Changes to task scheduling can impact individual buffer sizes, which in turn, would influence total buffer memory requirement. In case of Figure 3.1, for example,  $MT(C\_D, S_1) = 2$  and  $MT(C\_D, S_2) = 12$ . Note that under  $S_1$ , after production of 2 tokens by the actor C the consumer (D) gets fired, which consumes all of the existing tokens in the channel. Thus, the maximum number of tokens in the channel does not exceed 2. Unlike MT, the number of exchanged tokens over an edge does not depend on the schedule, and is only a function of the SDF structure and rates.

Efforts have been made in the past to minimize total buffer size via task schedule optimization. Bhattacharyya et al. present two effective algorithms for constructing a single appearance (SA) schedule with emphasis on reducing the memory requirement [BLM96]. Furthermore, phased scheduling has been proposed as a method for scheduling a SDF graph to minimize the memory size considering both code and data memory [KTA03].

In addition to scheduling, the data memory requirement is impacted by the scheme used to allocate individual buffers in the memory. In this work, we direct our attention to this problem, i.e., minimizing overall buffer size through improved buffer analysis and allocation techniques. That is, we seek to improve buffer management without perturbing the given schedule.

**3.1.3.** Buffer Sharing. In the baseline allocation scheme, separate portions of the memory are allocated to implement the channels of the SDF graph. During most of the execution time, however, the channel buffers are either partially or completely unused. For example in Figure 3.1, buffer  $A_{-}B$  is completely empty during the firings of H and I in the schedule S1. Therefore, the memory allocated to this buffer can be reused to implement buffer  $H_{-}I$ . That is, the two buffers can safely share at least one physical memory location during execution, without compromising the functionality of the streaming application.

Figure 3.2.B illustrates the synthesized code, under the buffer sharing assumption, for the example depicted in Figure 3.2. Buffers X, Y, Z and T are allocated at different offsets of the same array, called SB. Note that although buffers X and Z, and Y and T start at the same location in the shared buffer SB, the correctness of the computation is preserved. Extending the idea, any two channel buffers can be allocated to allow sharing of physical memory locations (space) as long as the two buffers do not conflict in time, i.e., if the two buffers do not need to maintain a token at the same memory location at the same time.

The software synthesis framework, including its code generation protocol, impacts the possibility of sharing between two buffers. In this work, we assume that code generation has to comply with the following rules:

- (1) None of the valid tokens of any buffer must be over-written or read by another buffer at anytime during the execution of the program.

- (2) Buffers must be statically allocated as contiguous regions in the application memory space.

- (3) The data cannot be moved around within the buffer, i.e., data production and consumption operations are the only primitives that can access buffers. Token production and consumption increment head and tail indexes, respectively.

The rules collectively guarantee that the generated code implements the functionality according to the SDF semantics. They eliminate the need for implementation of a complex inter-actor communication mechanism, which would incur large performance and code size

penalty. Outstanding examples of academic and commercial SDF synthesis frameworks follow the same basic principles [EJL<sup>+</sup>03, sim].

# 3.2. Granularity in Buffer Analysis

The SDF model of computation abstracts away the impact of intra-actor computations on synthesized software. That is, firing of an actor is viewed as the primitive execution operation in this model. Any valid schedule for a SDF gives the order and the number of firings of the actors. Using this sequence as a guideline, one can calculate the storage requirement (capacity) of buffers. Capacity of a buffer is time dependent due to firings of its producer, which adds tokens to the buffer and also firings of its consumer, which empties the buffer.

Such temporal changes, however, can be captured at different resolution levels [MB01]. The most accurate view of a buffer's temporal changes in storage requirement needs to follow the execution at the granularity of firing individual actors. In this scheme, execution of a task forms the unit of time for temporal analysis. We use the terms fine grain or highest resolution buffer analysis to refer to this level of abstraction.

Let "time step" refer to a unit of execution advancement at a given level of resolution. For example, a unit time step would refer to firing of an actor at fine granularity. For fine grain analysis we have:

$$T_{fg} = \sum_{v \in q_G} q_G[v]$$

$T_{fq}$ : Time step in fine granularity

$q_G$ : Repetition vector of graph G

where T denotes be the total number of time steps in one iteration of the schedule.

Nested loops make it possible to construct SA schedules in different forms. An actor might be executed in non-consecutive order, during one iteration of the SA schedule, depending on the presence and configuration of the nested loops. Note that the term "single appearance" only restricts the appearance of an actor in the closed form of the schedule.

To obtain the firing order of actors, and to accurately calculate the capacity of buffers at any time step, one has to unroll the nested loops and walk through the firing sequence of individual actors. However, one could compromise the accuracy in analysis of a buffer's temporal pattern, by avoiding to unroll all nested loops. Specifically, temporal changes to required capacity can be crudely and conservatively estimated. This leads to the *coarse* grain or lowest resolution temporal view of the buffer storage requirement, in which the buffer has the capacity MT(e, S) during its live range, and zero otherwise.

In coarse grain buffer analysis, not only loops are not unrolled, but all firings of the same actor are lumped together. That is, loop coefficients are distributed over the loop to arrive at a flat single appearance schedule. Relative to fine grain analysis, coarse grain analysis is conservative, since it allocates the maximum instantaneous memory requirement of a buffer throughout its life time.

The notion of time step at the coarse granularity refers to all firings of one actor. In other words, the coarse grain view is that all of q[v] firings of actor v occur in a single time step, whereas in fine grain it would happen in q[v] different time steps. Therefore:

$$T_{cq} = |V|$$

$T_{cq}$ : Time step in coarse granularity

There can be a number of middle grounds between the two ends of the granularity spectrum. One can unroll the loops according to their nesting depth to arrive at resolution levels that are in between the two extreme fine and coarse grain cases. Unrolling each level of nested loops would introduce more time steps for temporal buffer analysis, which in turn, increases the analysis and subsequent optimization complexity. However, the unrolling would relax the conservative view of buffer requirements, by refining the temporal characteristics of buffers, which potentially creates more opportunities for memory savings.

Varying the granularity of buffer analysis leads to different number of time steps for characterization of buffers' spatiotemporal patterns in the periodic schedule. Essentially, the time steps imply a schedule guideline (SG), which captures the actor firings that are embedded in each time step. SG is not the actual sequence of the firings according to the schedule, except in fine granularity analysis. It merely captures actor firings that are lumped together in time steps, according to the analysis resolution.

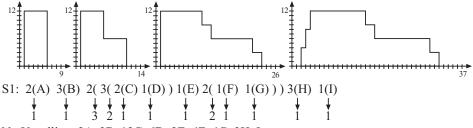

No Unrolling: 2A 3B 12C 6D 2E 4F 4G 3H I

Level 3: <u>2A 3B 6C 3D E 2F 2G 6C 3D E 2F 2G 3H I</u>

Level 2: <u>2A</u> <u>3B</u> <u>2C D 2C D 2C D E F G F G 2C D 2C D E F G F G 3H I</u>

Level 1: AABBBCCDCCDCCDEFGFGCCDCCDCCDEFGFGHHHI

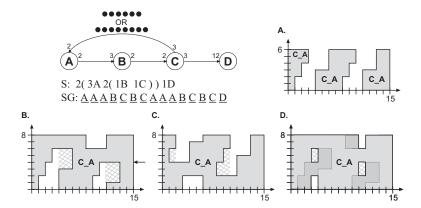

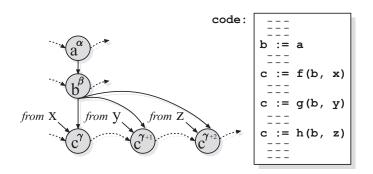

FIGURE 3.3. The impact of analysis granularity on characterization of buffer size  $B_{-}F$  (Figure 3.1 under  $S_1$ ). X and Y axis represent time steps and buffer size (number of its data tokens), respectively. Loops in the schedule are annotated with their nesting level, which are unrolled based on the analysis resolution to obtain the corresponding schedule guideline. In each level, a new Scheduling Guideline (SG) is given by unrolling the nesting loops marked with the same number or bigger in schedule  $S_1$ . The SG given in level 3 is the result of unrolling nesting loops (shown as parenthesis) marked with number 3. In level 2, the loops marked with numbers 2 and 3 are unrolled, and in level 1, loops marked with numbers 1, 2, and 3 are unrolled.

Figure 3.3 illustrates the impact of granularity in temporal analysis of buffer capacity for the buffer  $B_{-}F$  in Figure 3.1 under schedule  $S_1$ . It also shows the schedule guidelines used to characterize the temporal behavior. The size of required space for buffer  $B_{-}F$  grows with the firings of the producer actor B, and shrinks with the firings of the consumer actor F. For each level of granularity, the corresponding schedule guideline shows the actors that are fired in each time step, and their inter-time step order.

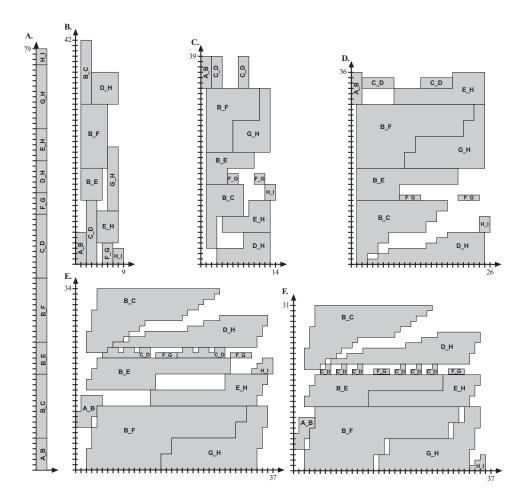

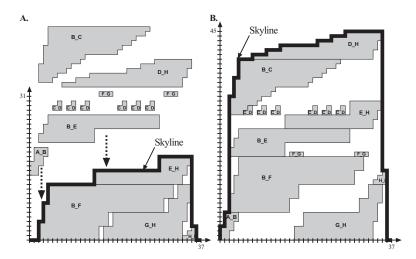

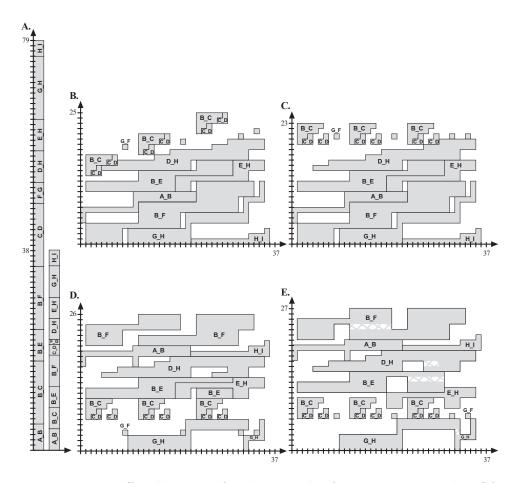

**3.2.1.** Visualizing Buffer Analysis and Allocation. Buffer analysis characterizes buffers' spatiotemporal footprint in a two-dimensional plane, in which the X-axis shows time steps, and the Y-axis represents the required storage size. As a result, buffer allocation can be viewed as placement of buffer's spatiotemporal footprint in the plane, with the minor adjustment that the Y-axis has to represent an offset in the shared memory space. Figure 3.4 visualizes buffer allocations, for the SDF example of Figure 3.1 under schedule  $S_1$ .

The gray area of each buffer illustrates the range between head and tail indices that contains valid data. The temporal update in the gray area is due to the production and consumption operations, which increment the head and tail indices, respectively. The buffers are indexed relative to an *offset*, which indicates the start of the buffer within the shared space.

For a given analysis granularity, the capacity requirement of a buffer at any point in time is fixed. Thus, the X coordinate of buffers in the two dimensional time-memory plane cannot be modified. The Y coordinate, however, represents the physical location of the allocated memory to implement the buffers. Thus, the memory allocation problem can be viewed as geometric layout of buffer polygons, in which a solution is valid if the *laid out* buffers do not conflict in the time-memory plane. The only operation for perturbing the layout is vertical movement of the buffers. The geometric placement of a buffer in the plane readily gives its offset in the memory space. The optimization objective is to minimize the vertical dimension of the layout, which represents the total memory allocated to buffers.

**3.2.2.** Impact of Granularity on Buffer Allocation. The granularity in buffer analysis compromises accuracy in capturing temporal behavior of buffers with analysis and subsequent allocation complexity. Moving from coarse-grain to fine-grain analysis on the complexity spectrum, improves temporal details that enable more opportunities for buffer sharing at the cost of longer optimization runtime. The layouts in the Figure 3.4 illustrate the idea.

Figure 3.4.A shows the baseline buffer allocation scheme in which, buffers are assumed to have maximum capacity throughout the execution. Thus, they cannot share any locations during the runtime, and have to be allocated in separate locations. The Figure shows that the total size of buffers is 79.

Figure 3.4.B depicts the optimal allocation, when buffers are analyzed at the coarse granularity. This corresponds to the "no unrolling" case in Figure 3.3. In this scheme, buffers are assumed to have maximum capacity throughout their live range in the schedule. For example  $MT(A\_B, S_1) = 6$ , and under the coarse-grain analysis model six memory cells have to be allocated during its entire life time to implement this buffer. Thus, two buffers would conflict if they are alive in at least one point in time in which case, they cannot share any physical memory location and have to be allocated in distinct memory spaces. Live range is naturally defined over coarse grain "time steps". Under coarse grain analysis, the optimal total size of channel buffers is 42 (Figure 3.4.B).

FIGURE 3.4. Buffer allocations for the example of Figure 3.1 under  $S_1$ : **A.** Baseline **B.** Coarse grain **C.&D.** Two possible in-between analysis points **E.**Fine grain **F.** Fine grain combined with buffer merging. X and Y axis show time steps and the offset within the shared memory space, respectively.

Figures 3.4.C and D present optimal buffer allocation for two levels of granularity in the middle of the spectrum. They correspond to levels 3 and 2 in the example of Figure 3.3. The total size of channel buffers is 39 and 36, correspondingly.

Finally, Figure 3.4.E shows the optimal allocation of buffers under fine grain analysis scheme, in which, buffers' temporal behavior is updated at the granularity of actor firings (Level 1 in Figure 3.3). Intuitively, fine-grain view of the buffers' spatiotemporal patterns enables more condensed packing of the buffers in the memory, which translates into smaller code size. In this example, the total size of channel buffers is 34.

The examples clearly demonstrate the tradeoff between complexity and quality of the allocation process, which is introduced by analysis granularity. Intuitively, as the number

of time steps increases the solution space becomes more complex, however it creates opportunity for denser packing of the polygons in the plane. We will study the tradeoff more closely in the subsequent Sections.

3.2.3. Buffer Characterization During Actor Execution. Our discussion so far has focused on analysis of buffers temporal capacity pattern at the boundary of actor firings. The SDF semantics is explicit in requiring input data being available upon firing; and input/output tokens being consumed/generated upon termination of the firing. Depending on the code generation assumptions that govern the timing of token consumption and production "during" execution of an actor, one might be able to refine the buffers further.

For simplicity, let us assume that actor v has an incoming edge  $e_i$ , and an outgoing edge  $e_o$ . For actor v to be executable, there must be at least  $cns(e_i)$  tokens on  $e_i$ . Firing of actor v consumes  $cns(e_i)$  tokens from  $e_i$ , and produces prod(e) tokens on  $e_o$ . In the absence of any information on actor computation or code generation optimizations, one must assume that the input tokens have to remain valid during the execution of the actor. Similarly, it must be conservatively assumed that output tokens can be generated at anytime during the execution, and not necessarily upon its termination. Hence,  $cns(e_i)$  and  $prod(e_o)$  capacity should be allocated on  $e_i$  and  $e_o$ , respectively, during the time step of firing. Upon termination of the actor execution, the corresponding memory on  $e_i$  will become available, while  $e_o$  will have to retain the data until its consumer fires.

On another hand, it is possible that input tokens are consumed before generation of any output token. For instance, the code generation scheme might synthesize code to transfer the input tokens to local storage upon firing. As another example, the actor's specific computation might consume all input tokens before generating the output tokens. In such cases, the memory space on  $e_i$  could be used to store the produced tokens on  $e_o$ . This optimization is known as buffer merging [MB04].<sup>3</sup>.

We use the term buffer merging to imply the assumption that actors locally store all their input tokens at the beginning of their execution, which in effect reduces the capacity of the input buffer upon firing of the consumer actor. This assumption is equivalent to assuming CBP = 0 in [MB04, BM04]. That is, the requirement to retain input tokens

<sup>&</sup>lt;sup>3</sup>A complete merging would be also applicable if an actor iteratively consumes x input tokens to generate y output tokens, where  $x \ge y$ . All actors in the example of Figure 3.2 have this property.

during the execution of an actor would be relaxed under this assumption. The temporal variation in output buffers upon firing of producer actors remains unaffected.

Figure 3.4.F illustrates the impact of considering buffer merging during the allocation process. Assuming that buffer merging is available, buffers  $B\_E$  and  $E\_H$  can share their entire memory space, while without the merging assumption (Figure 3.4.E) this was not possible. Similar impact can be observed for buffers  $A\_B$  and  $B\_F$ , and also  $G\_H$  and  $H\_I$ , although in these two cases, the denser packing of polygons does not affect the total size of channel buffers. The optimal total size of buffers is reduced to 31.

Note that merging becomes possible when buffers are analyzed at the fine granularity in which, only one actor is fired in each time step. In the coarse grain or any in-between analysis, time steps do not have a one-to-one relationship with actor firings. Hence, combining merging with buffer sharing at those resolution levels would lead to incorrect implementations.

#### 3.3. Buffer Allocation Problem

The temporal behavior of FIFO buffers can be characterized with a pair of  $\underline{\mathbf{H}}$ ead and  $\mathrm{tai}\underline{\mathbf{L}}$  vectors. H and L refer to the head index  $H_e[t]$  and  $\mathrm{tail}$  index  $L_e[t]$  at time step t of the schedule guideline, respectively (Section 3.2). Thus, the length of H and L are equal to the number of time steps, which depends on the analysis resolution. In the case of the reference model, head and tail indices periodically start from zero and are incremented upon write or read operations, until they reach their maximum size of MT(e, S). Formally:

$$\forall e \in E : B_e = (H_e, L_e)$$

$B_e$ : Buffer of edge e, or buffer e in short

$H_e[t]$ : Head index at time  $0 \le t \le T$  for  $B_e$

$L_e[t]$ : Tail index at time  $0 \le t \le T$  for  $B_e$

$T_{cg} \leq T \leq T_{fg}$  (cg. coarse grain - fg. fine grain)

The objective of buffer allocation is to assign an offset within the shared buffer space to each buffer. The offset has to be added to head and tail indices, the relative displacement within the buffer, to access the memory for read or write operations. Let vector O denote

the offset values for all the buffers of the SDF:

$$O = \{(o_{e_1}, o_{e_2}, o_{e_3}, \dots, o_{e_M}) \mid e_1 : e_M \in E , M = |E|\}$$

$$o_e \text{is the offset for buffer } e$$

Given vectors H and L, the shared buffer size (SBS) can be formally stated as:

$$SBS = \max_{\forall e \in E} \{ o_e + H_e^{max} \mid H_e^{max} = \max_{0 \le t \le T} (H_e[t]) \}$$

The following Lemma specifies an important relationship between head and tail indices:

Lemma 3.1. Under the reference model (zero initial tokens on SDF edges, and single-appearance task execution schedule), the head index is always greater than or equal to the tail index in the same time step:  $\forall t \leq T : H_e[t] \geq L_e[t]$

Given a consistent SDF graph and a valid SA schedule, one can determine the vectors H and L. Subsequently, the objective of the buffer allocation problem is to determine the offset vector O, such that SBS is minimized, and the following constraint is satisfied:

$$\forall a, b \in E$$

$$\forall 0 \le t \le T, if H_a[t], L_a[t], H_b[t], and L_b[t] \ne 0:$$

$$H_a[t] + o_a \le L_b[t] + o_b OR H_b[t] + o_b \le L_a[t] + o_a$$

The constraint ensures that no buffer can write to, or read from valid data of another buffer that is alive at the same time. Therefore, for buffer e at any time during its live range, other buffers have to be allocated before or after e in the memory. The offsets are determined statically and will not change in runtime. The static nature of the SDF guarantees that compile time calculation of offsets will lead to safe execution. Note that the formulation is applicable to all levels of granularity. The analysis granularity determines T, and head and tail indices in each time step.

#### 3.4. ILP Formulation

Integer Linear Programming (ILP) provides a mechanism to obtain the optimal solution of a problem as long as its constraints and objective can be described as linear expression of integer variables. Since there are many commercial ILP solvers available, one only has to cast the problem in ILP formulation to solve a specific instance. In case of the buffer sharing problem, linear constraints have to ensure that all buffers are allocated without any conflict.

The subtle difficulty in such formulation is to avoid buffer conflicts using linear constraints, because two conflicting buffers can be allocated in either order in the shared buffer. In other words, formulation of the "OR" logic is non-trivial, since a buffer can be allocated either before or after another conflicting buffer as long as there is no violations of the stated guidelines.

Because linear constraints cannot be easily used to articulate the "OR" logic, we had to reformulate the problem. For each buffer and each location in the shared memory space, specifically, we define a binary variables, whose '1' value would indicate allocation of the buffer in the corresponding memory location. Subsequently, buffer conflict constraints can be formulated as a large number of linear constraints that have to be generated for all time steps.

Let BBS refer to the baseline buffer size (Figure 3.4.A). BBS is known from static analysis, and is an upper bound on the shared buffer size (SBS):

$$BBS = \sum_{e \in E} MT(e, S)$$

We define the following variables to represent the head index:

$$\forall e \in E \ \forall 0 \le i \le BBS \ \forall 0 \le t \le T :$$

$$h_{e,i,t} = \begin{cases} 1 \ \text{if } H_e[t] + o_e = i \\ 0 \ \text{otherwise} \end{cases}$$

The idea is to have a binary variable for every location of the shared buffer to determine if the head index of buffer e is pointing to the location i of the shared buffer at the time t.

We also define variable o to represent the offset values of the buffers. Note that since the offset values for buffers do not change throughout the entire program, there is no index of time in their definition:

$$\forall e \in E \ \forall 0 \le i \le BBS$$

$$o_{e,i} = \begin{cases} 1 & \text{if } o_e = i \\ 0 & \text{otherwise} \end{cases}$$

Vectors H and L are given, thus the number of tokens that exist in buffer e at any given point in time is known. We use variable  $S_e[t]$  to refer to size of buffer e at the time t.  $S_e[t]$  can be simply calculated by measuring the gap between head and tail at all points in time.

$$S_e[t] = H_e[t] - L_e[t]$$

Recall that the maximum size of buffer e in schedule S is MT(e,S) ( $MT_e$  for short since we are not changing the schedule in this problem). Having defined the above variables and constants, the constraints of the problem can be stated as the followings:

(1) Each buffer must be allocated exactly once:

$$\forall e \in E : \sum_{i=0}^{BBS-MT_e} o_{e,i} = 1$$

Notice that  $BBS - MT_e$  is the last possible location in the shared buffer for allocation of buffer e.

(2) At any time t, the head index points to exactly one location:

$$\forall e \in E \ \forall 0 \le t < T : \sum_{i=0}^{BBS} h_{e,i,t} = 1$$

(3) Buffers that are alive at the same time must not conflict. That is for two buffers a and b that are both alive at time t, if head of buffer b points to location i, head of buffer a cannot point to locations between i and the tail of buffer b:

$$\forall co-existing \ a,b \in E \ \forall 0 \leq i < BBS \ \forall 0 \leq t < T :$$

$$h_{a,(i-S_a[t]),t} + \sum_{j=i-S_a[t]}^{i-1} h_{b,j,t} \le 1$$

This constraint does not enforce buffer a to be assigned to index i. It ensure that if it was assigned, no conflicting buffer could have its head assigned to its live range at the same time.

(4) The relationship between a buffer's offset, head and its size are known at each point in time:

$$\forall e \in E \ \forall 0 \le i < BBS \ \forall 0 \le t < T : o_{e,i} = h_{e,(i+S_e[t]),t}$$

Note that we are only interested in finding out the offsets. The head variable is merely an auxiliary variable, which facilitates articulation of problem constraints. Once offsets are determined, the head variables are readily available.

(5) The following equation gives a lower bound on SBS. Minimizing this equation with consideration to other constraints will minimize SBS, which is the objective of the allocation problem:

$$\forall e \in E : MT_e + \sum_{i=0}^{BBS} i \times o_{e,i} \leq SBS$$

The complexity of buffer sharing ILP instance and the solver runtime grow exponentially with problem complexity. Therefore, ILP does not provide a scalable approach to solving the problem. Nevertheless, we utilize it to obtain the optimal solution to problem instances, although at the cost of unreasonably long solver runtime, primarily for evaluation of our proposed technique through measurement of the optimality gap (Section 3.9).

# 3.5. Strip Packing Problem and Buffer-Sharing

Buffer allocation can be viewed as a special packing of 2-dimensional polygons on the plane. Similar problems have been studied in several other industries, where there is a need for packing a set of 2-dimensional objects on a larger rectangular unit of material to minimize the waste. This larger unit can be a standardized sheet of material, from which the set of objects have to be cut. The objective is to pack all the items into the minimum number of units. This problem is a variation of the well-known bin-packing (BP) problem, and arises in some industrial applications such as wood or glass industries.

In other contexts the standardized unit is a roll of material such as a roll of paper or cloth, and the objective is to use the minimum roll length. This problem is called strippacking (SP) problem, which is akin to the formulated buffer sharing problem. Both of these problems are known to be NP-complete, and there has been various attempts to solve them in the algorithms community [LMM03].

In the context of buffer sharing one can realize a large array of memory (which we call shared buffer) analogous to the roll of material in the SP problems, and the different buffers on different edges of the graph could be the set of objects. Figure 3.4 shows the geometrical aspect of buffers where we have time on one axis and the indices of shared-buffer on the other axis. In this model the objects are being constructed from the number of tokens that exist in the buffer during the run time of the program. Subsequently, we adopt a SP packing algorithm proposed in [Jak96] with some adjustments specific to the buffer sharing problem.

# 3.6. Evolutionary Buffer Optimization

Using the same concept as in 3.5, in this Section we propose an evolutionary genetic optimization technique to solve the buffer allocation problem. Our approach is to associate a cost to every sequence of buffers, and then, perturb the sequence via evolutionary optimization to improve quality.

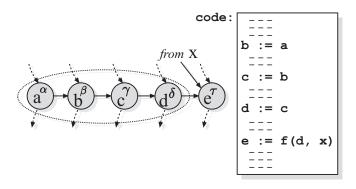

**3.6.1.** Buffer Size Calculation via Move Down. Recall that buffer allocation can be transformed to a special version of 2-d packing of buffer polygons. In the packing instance, objects can only be moved vertically but not horizontally. Vertical relationship of objects in the layout can be viewed to define an order among buffers.

In particular, we take a sequence of buffers to define the order in which, the buffers are introduced to the 2-d packing problem. The associated cost, i.e. buffer size, of the order can be calculated by  $moving\ down$  the objects (buffers) toward the Y axis (beginning of the shared-buffer array) as much as possible. The packing becomes as dense as possible, for the given ordering, with the move down operation.

Move Down Algorithm (MDA) is our method for evaluation of the quality (buffer size) of a given sequence of buffers. Therefore, it will be iteratively executed during the run time of the evolutionary optimization algorithm. Figure 3.5 shows that the order of moving

FIGURE 3.5. The impact of ordering on total buffer size for the example of Figure 3.1 under  $S_1$  **A.** Move down of the buffers in the shown order will result in the optimal solution of Figure 3.4.F. **B.** A sub-optimal permutation:  $(G_-H, A_-B, H_-I, B_-F, F_-G, B_-E, E_-H, C_-D, B_-C, D_-H)$ . The bold line shows the skyline.

down the buffers impacts the total buffer size. The sequence of buffers illustrated in Figure 3.5.A would lead to the allocation depicted in Figure 3.4.F. The sequence shown in Figure 3.5.B yields uncompetitive results.

To understand how far a buffer can go down we introduce another vector which is called skyline and denoted Vsk[t]. Here we consider buffers as solid polygons, which can stand on top of each other to construct a wall. Looking this way, skyline is the contour defined by the highest level of the constructed wall. Figure 3.5 shows two different skylines.

To construct the skyline vector we introduce skyline function which takes a Vsk and buffer  $B_e$  and also an offset o to place the buffer, and it will calculate the skyline vector  $\acute{V}sk$  constructed from adding the new buffer at the point o to the existing skyline.

$$\forall e \in E \ \forall 0 \le o \le BBS \ \forall 0 \le t < T :$$

$$\acute{V}sk = skyline(Vsk, e, o) = \begin{cases} Vsk & \text{if } S_e[t] = 0 \\ h_e[t] + o & \text{otherwise} \end{cases}$$

MDA takes a skyline vector and a buffer, and returns the lowest offset it can get from pushing down this buffer before hitting the skyline.

$$o_e = MDA(Vsk, B_e)$$

The algorithm first places the buffer on the first level of the skyline by setting the offset to Vsk[0]. Then moving to the right, it compares the skyline to the seated buffer to see if there is any conflict and if there is one, it will adjust the offset to remove the conflict. At the end the algorithm returns the calculated offset which does not cause any conflict with any other buffer throughout the entire program.

If we run MDA on all the buffers in a pre-defined order, and also calculate the skyline on each step and use it for the next step, we have done the buffer allocation. We call the pre-defined order a permutation of buffers and denote it with  $\pi$ . The function placeAll will then place each buffer in the same order they have in  $\pi$ .

The first buffer always gets zero for the offset, and it is because we are pushing down the buffers as much as possible and there is nothing in the shared-buffer yet so it goes all the way down. The very first skyline vector is  $V_{zero} = [0, 0, ..., 0]$  which we can consider the ground. The second skyline forms when we push the first buffer down to the ground. Therefore skyline forms exactly on the top of this buffer which is the vector H. The final skyline is  $Vsk_{M+1}$  and determines the height of the wall which is actually the size of shared-buffer:

$$SBS = \max_{0 \le t \le T} (Vsk_{M+1}[t])$$

The size of shared-buffer depends on the sequence of buffers we are using, and PlaceAll itself does not guarantee that it will give us the optimal solution. However because it uses the notion of sequence in placing the buffers, it reduces the search space from  $(BBS)^M$  (all the possible places for M buffers to be in an array with the size of BBS) to M! (the number of different sequence of buffers that we can have). Moreover having a sequence of data as the input, is one of the fundamentals of a genetic algorithm and enables us to use them to find the optimal or near optimal solution. Algorithm 3 uses placeAll combined with the evolutionary part (which will be discuss in 3.6.2) to solve the buffer allocation problem.

Lastly in this Section, the following Lemma shows the MDA capability of giving us the optimal solution for the reference model:

Lemma 3.2. The MDA transforms the buffer allocation problem into finding the right sequence of buffers. In particular under the reference SDF model (zero initial tokens on SDF edges, and single-appearance task execution schedule), there exist a sequence of buffers, which gives their optimal allocation using MDA.

Extensions to other cases other than the reference model are discussed in Section 3.7.

3.6.2. Sequence Evolution using Genetic Optimization. We utilize the move down principle to construct an evolutionary genetic optimization technique. Genetic optimization is composed of several key components, including chromosome, inheritance and fitness function. Chromosome provides an abstract representation of solutions in the search space, and is normally represented as a sequence of numbers. Inheritance models the basic operations through which, chromosomes are perturbed to improve the solution quality. Typically, there are two crossover and mutation inheritance operations in a genetic optimization framework. Finally, the fitness function quantifies the "quality" of candidate solutions, and determines survival of selected candidates. Our objective is to define the notions of chromosome, inheritance and fitness, in the context of buffer sharing, and subsequently, utilize genetic optimization to solve our problem at hand.

MDA provides the ability to work on a sequence of buffers as the input (chromosome) and to allocate all of them inside the shared buffer according to their order in the sequence (Subsection 3.6.1). The size of the shared buffer is the height of the final structure, in the corresponding packing instance. We propose to use different permutations of buffers as chromosomes, or individuals of a population, and the height of the final skyline as the fitness function, in the genetic optimization framework. Consequently, the algorithm will work in the following steps:

To initialize the algorithm with a sample population, we randomly select a set of permutations. The size of the sample population is a pre-defined parameter. We used the number of buffers (M = |E|) to be the size of the population in our algorithm.

Sample set =

$$\{\pi_1, \pi_2, \pi_3, ..., \pi_M\}$$

Since genetic algorithm keeps track of different lines of breeding patterns, having a larger sample population gives us the ability to keep track of more candidate solutions. On the other hand, having a very large population slows down the algorithm, and reduces the chance of finding the optimal solution in a reasonable time.

Now we can run PlaceAll algorithm and calculate the height of the final solution in every individual permutation in the set. We choose the height of each permutation (denoted as  $height(\pi)$ ) to be the fitness function (denoted as  $f(\pi)$ ) as follows:

$$f(\pi) = \frac{1}{height(\pi)}$$

For any permutation there is a chance that part of its sequence matches the sequence in the optimal solution. Basically, we would like to find these parts from different members and concatenate them, so that we can get closer to the optimum. The mechanism to recognize if we are getting closer to this goal is the fitness function. To generate new members first we need to select two of the existing members, which we refer to as parents. We select the parents depending on their fitness. The fitter individuals (shorter in height), have a higher chance of being selected. The probability of selection of an individual permutation (denoted as  $p(\pi)$  is likely to change in each iteration of the algorithm due to changes to the fitness of the other members of the group.

$$p(\pi_i) = \frac{f(\pi_i)}{\sum_{j=1}^{M} f(\pi_j)}$$

In practice we can divide the interval [0,1) into M sub-intervals as follows:

$$[0, p(\pi_1))$$

,  $[p(\pi_1), p(\pi_2))$ , ...,  $[p(\pi_{M-1}), p(\pi_M))$

Two random numbers from the interval [0,1) will determine the selected permutations.

Subsequently, the parent chromosomes are used to create the children using the crossover operation. Our crossover function generates two random numbers  $1 \le p \le q \le M$ . Then it copies the sub-sequence of the first parent from position p to q, and place it at the beginning of the child's chromosome. The sequence from p to q is the part that we would like to preserve, hoping that the same sequence exists in the optimal solution. Finally, we fill the rest of the offspring with the remaining genes (buffers) in the second parent in the same order that they appear in the second parent. The following example shows how

crossover function works:

$$p = 2 \ q = 4$$

$$\pi_{parent1} = (B_{e1}, \mathbf{B}_{e2}, \mathbf{B}_{e3}, \mathbf{B}_{e4}, B_{e5}, B_{e6})$$

$$\pi_{parent2} = (\mathbf{B}_{e6}, \mathbf{B}_{e5}, B_{e4}, B_{e3}, B_{e2}, \mathbf{B}_{e1})$$

$$\pi_{child} = (B_{e2}, B_{e3}, B_{e4}, B_{e6}, B_{e5}, B_{e1})$$

Copying and matching different sequences from existing permutation may lead the process to stay in a local minimum region. To avoid this situation we can mutate the child based on the probability  $p_{mutation}$ , which is another parameter of the algorithm. If the child is to be mutated, then the function generates two random numbers  $1 \le i, j \le M$ , and swaps the buffers in those positions within the sequence.

$$p_{mutation} = 0.4$$

: the probability of being mutated  $i = 2$   $j = 4$

$$\pi_{child} \text{ Before } = (B_{e2}, \mathbf{B}_{e3}, B_{e4}, \mathbf{B}_{e6}, B_{e5}, B_{e1})$$

$$\pi_{child} \text{ After } = (B_{e2}, B_{e6}, B_{e4}, B_{e3}, B_{e5}, B_{e1})$$

The *PlaceAll* algorithm is run on the newly generated child to calculate the height of the offspring. The child is then added to the population set. To maintain the pre-defined population of the sample set we kill (remove) the weakest (highest) member of the sample set. Therefore the offspring will be compared against the weakest member of the population, and may or may not remain in the sample set.

Iteratively, we generate new children and compare them to the existing members until the termination point where we can return the best solution found. Termination can be an acceptable size of the shared buffer (the height of the best permutation). Alternatively, the optimization can be terminated at a time limit. We selected the number of iterations as the termination criterion. We set the value to be the product of M and an iteration parameter.

## Algorithm 1 Evolutionary Buffer Allocation

```

/* M : number of buffers */

/* O[1..M] : offsets */

/* f[1..M] : fitness functions */

sampleSet [1..M] = createRandomSamples( M ) /* generates M different permutations

of buffers */

for i = 1 to M do

(O[i], f[i]) = placeAll(sampleSet[i])

end for

while !termination() do

parents = pickParents( sampleSet ) /* randomly selects two permutations based on

their fitness function */

newBorn = crossOverFunction( parents ) /* applies crossover function on the two

parents to generate the newborn */

newBorn = mutate( newBorn ) /* mutates the newborn based on the mutation proba-

bility */

(O_{newBorn}, f_{newBorn}) = \text{placeAll( newBorn)}

f_{min} \leftarrow \min_{i=1}^{m} f[i]

if f_{newBorn} \geq f_{min} then

replace newBorn by samplesSet[ min ]

else

discard newBorn

end if

end while

f_{best} \leftarrow \max_{i=1}^{M} f[i]

return O_{best}

```

## 3.7. Extension of The Reference Model

We present two extensions to the reference model that was used in our discussions so far. Specifically, we consider non-single appearance task schedules and initial tokens on the edges of SDF graphs. We highlight the implications of these two extensions for our proposed buffer allocation technique, through which, we establish its applicability beyond the reference model.

**3.7.1.** Non-Single Appearance Schedules. Changing the task firing schedule results in characterization of polygons with different shape and size. Under SA schedules, the producer fills in the buffer and then the consumer completely empties it (Figure 3.2.A). Therefore, the first post-consumer firing of a producer writes to an empty buffer. Under non-single appearance (nSA) schedules, however, the producer might fire after the consumer in a period, while the buffer is not *completely* empty between the two firings.

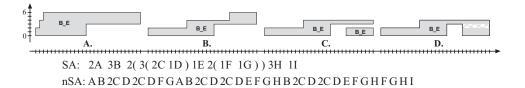

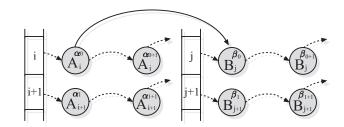

FIGURE 3.6. Geometrical characterization of buffer B\_E in the example SDF of Figure 3.1, under: **A.** The given SA schedule **B, C.** The given nSA schedule assuming linear and ring FIFO implementation, respectively **D.** Conservative approximation of the ring buffer.

In addition to task schedule, the indexing strategy that the synthesizer uses to implement the buffers, impacts characterization of polygons. Buffers are typically implemented as linear or ring (circular) FIFO arrays in the synthesized software. In linear FIFOs the head and tail indices are consistently incremented in a period, whereas in ring FIFOs they might reset within the periodic schedule after reaching a maximum index.

In linear FIFOs, thus, the head index would always be greater than or equal to the tail index. In ring FIFO implementations, however, if the head index reaches its maximum value it would wrap around to the beginning to continue the write operation. As this could happen within the period of a nSA schedule, it is possible that the head index would become smaller than the tail index during the period. Lemma 3.1 does not hold under such code generation policy. Note that one must use ring buffers to bound the size of buffer e to MT(e, S), under non-single appearance schedules.

Figures 3.6.A through 3.6.C depict several characterizations of buffer  $B\_E$ , for the example SDF of Figure 3.1. While buffer in Figure 3.6.A is characterized under a SA schedule, Figures 3.6.B and 3.6.C illustrate the difference in characterization of the polygons under the two linear and ring buffer implementation strategies. Figure 3.7 shows the impact of linear and ring buffer implementation on the synthesized code for the example SDF of Figure 3.2, under the shown nSA schedule.

We proceed to highlight the implication of nSA schedules for our approach under three different buffer implementation strategies:

3.7.1.1. Linear FIFO Implementation. In linear buffer implementation, the head index is always greater than or equal to the tail index. Therefore, buffer characterization using head and tail indices as top and bottom borders yields solid polygons similar to the case of SA schedules, although the size of the buffer might be larger than MT(e, S) (3.6.B).

FIGURE 3.7. The synthesized code from the SDF in Figure 3.2 under the given nSA and buffer implementation A. linear FIFOs B. ring FIFOs

By solid we mean to imply that the polygons do not surround empty spaces that would be unreachable by MDA. As a result, Lemma 3.2 still holds, and MDA continues to be effective for packing a given sequence of such buffers. That is, the packing problem remains a matter of finding the right sequence of buffers presented to the MDA. Figure 3.8.B illustrates the optimal buffer allocation for our working example that is obtained by MDA under linear FIFO implementation assumption.

3.7.1.2. Ring FIFO Implementation. As the head index might wrap around within the periodic schedule, it could become smaller than the tail index. Thus, the characterized buffer polygons might surround empty spaces (Figure 3.6.C). It follows that in this case, the head and the tail indices do not necessarily represent top and bottom borders of the extracted geometrical object at all times, and Lemma 3.2 no longer holds. MDA would be unable to correctly pack a given sequence of such polygons, as it cannot reach the surrounded empty space.

One approach to solve this issue is to make the empty spaces within the characterized buffer polygons unavailable for sharing using bounding polygons (Figure 3.6.D). This conservative approximation enables the MDA to pack a given sequence of polygons. Although the resulting solution may lose some optimization opportunity due to the introduced inaccuracy, it is likely that the overall process would significantly reduce total buffer size. Figures 3.8.D and 3.8.E illustrate the optimal solution for our working example, obtained via hand

FIGURE 3.8. Buffer allocations for the example of Figure 3.1 under the nSA schedule in Figure 3.6: **A.** Baseline using linear and ring FIFO implementations **B.** Using MDA for linear FIFOs **C.** Using MDA for a hybrid implementation **D.** Hand optimized for ring FIFOs **E.** Using MDA for conservatively characterized ring FIFOs

optimization and via the MDA-generated solution after conservative approximation of the objects, respectively.

3.7.1.3. Hybrid Implementation. The amount of memory saving greatly depends on the ability of the characterized geometrical shapes to admit dense packing in 2-D space. A hybrid technique enables us to decide which combination of different buffer implementation strategies yields a better result. That is, implementing some buffers as ring FIFO and some as linear FIFO might be superior to adoption of only one implementation strategy for all buffers of the SDF. Searching through different combination of buffer implementations is beyond the scope of this dissertation, however, there are some intuitive hybrid approaches that are likely to reduce the memory footprint. For example Figure 3.8.C shows a packing of buffers using MDA, where a linear FIFO is used to implement a buffer unless it becomes

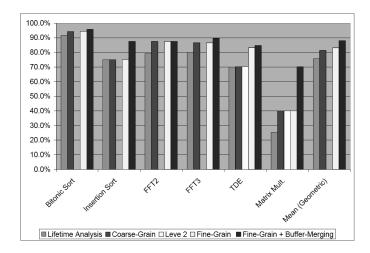

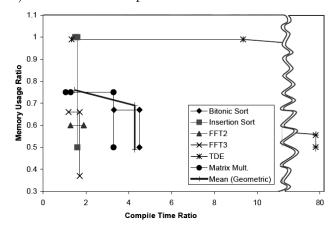

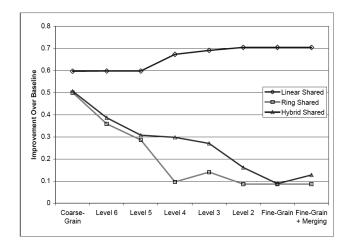

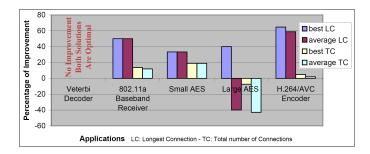

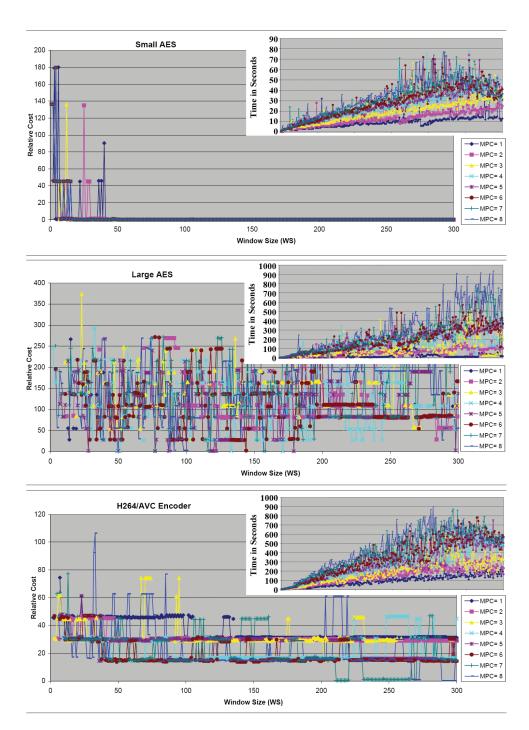

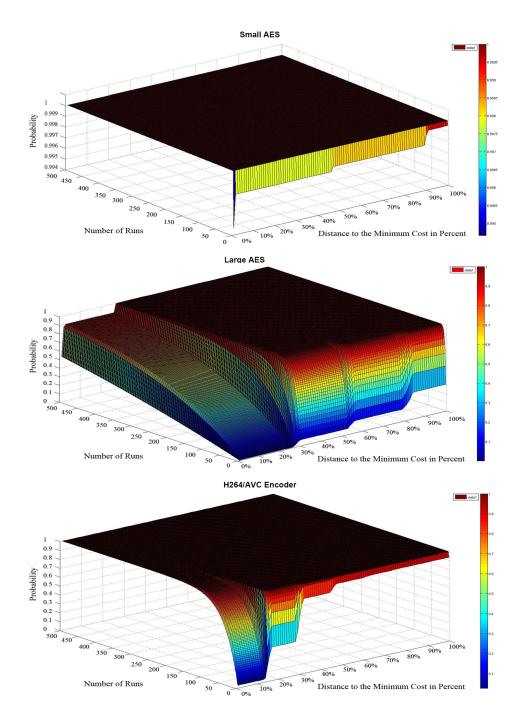

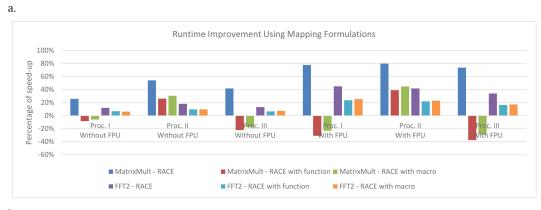

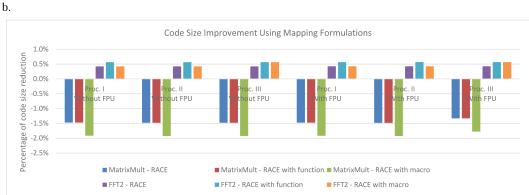

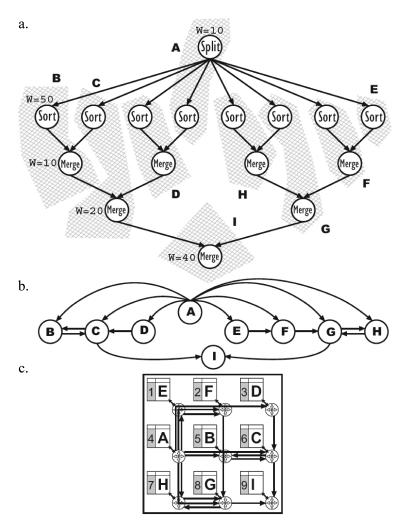

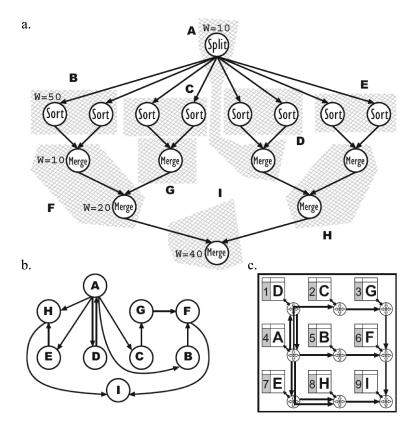

empty within the periodic schedule. If the buffer becomes empty during the period, we reset both head and the tail indices to the beginning of buffer, making it a ring buffer. Since our proposed buffer allocation scheme is applicable to both linear and ring FIFOs, it remains effective for hybrid implementations as well.